Hello,

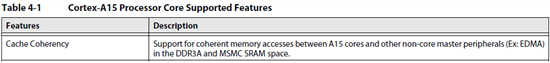

I would like to confirm about EDMA access on 66AK2Hxx.

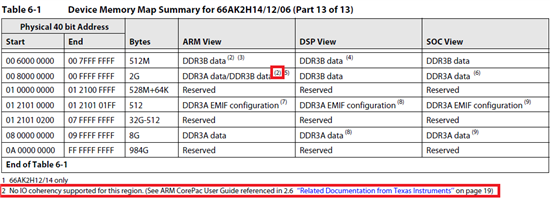

I am seeing the Memory map summary of 66AK2Hxx(sprs866e: P93).

It seems that :

- The EDMA(SoC master) can access only the first 512MB of DDR3B.

- The EDMA can NOT access all of the DDR3B area(2GB).

Is that right?

Best regards, RY