Hi,

Please let me confirm the following questions.

1. What kinds of XF pin status is assumed when perform the reset to C5535/C5515 or the POWERGOOD signal is "Low"?

i.e. I would like to know whether XF pin will be unstable(X).

2. If assumed that XF pin will be both status "H" and "L", is it potential that the XF pin behavior will change by the timing of dropping the voltage VDD_PLL and DSP_LDO?

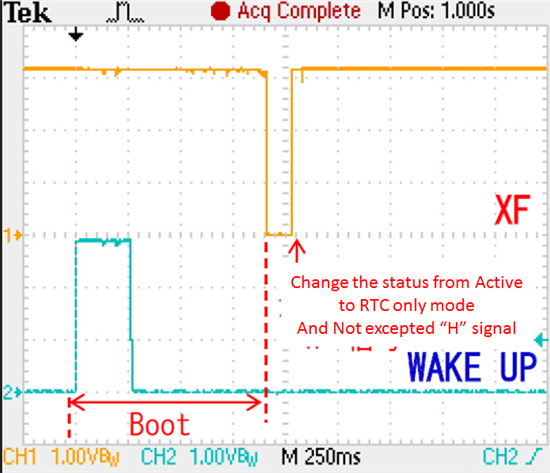

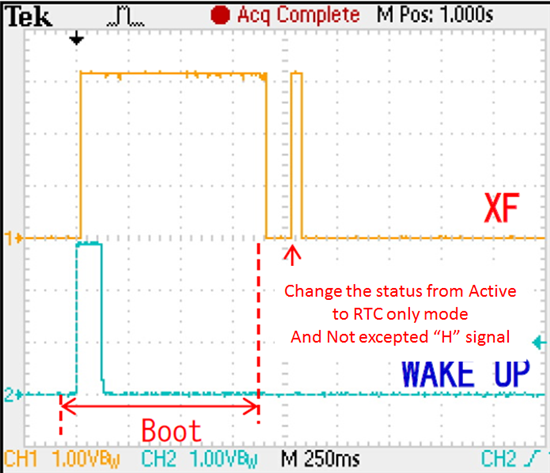

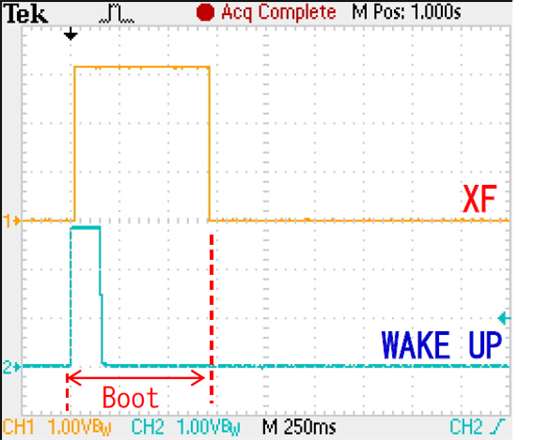

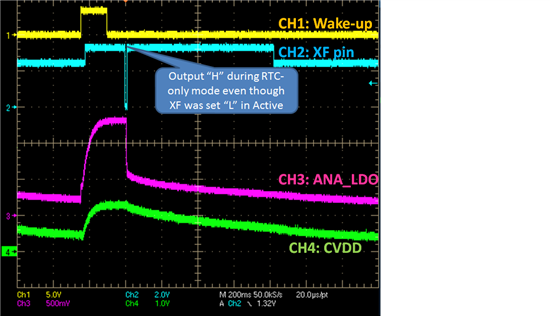

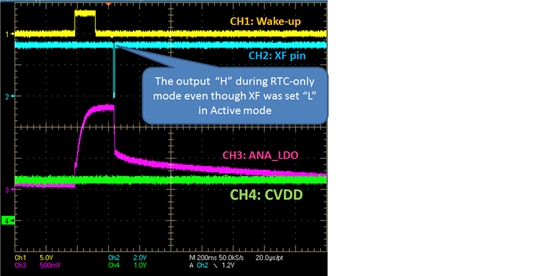

According to the customer's board, if the DSP_LDO powered down after the VDD_PLL(i.e. Change the status from active to RTC only mode), XF pin was generated the "H" even though the S/W did not set the register of XF. In addition to this, If the DSP_LDO will power down before the VDD_PLL, this phenomenon did not confirm.

I attached this waveform as below.

Sometimes, this "H" signal did not appear on XF pin.

If you have any questions, please let me know.

Best regards.

Kaka