Hi all,

**********************************************************************************

I want to test the DDR3 bandwidth.

In the beginning, I used the codes below to test if the DDR3 controller's configuration was OK.

while(1)

{

*(DDR3_ADDR) = temp_w;//w

temp_r = *(DDR3_ADDR);//r

if(temp_w == temp_r)

break;

temp_w++;

DDR3_ADDR++;

}

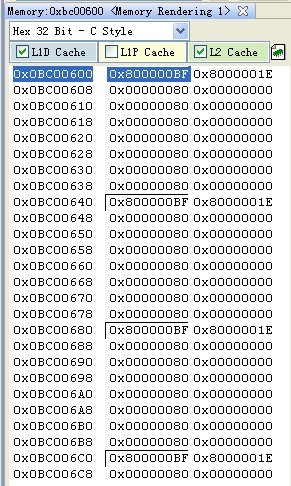

Then the test was OK and I could find the data I wanted to write into the DDR3 using Memory Broswer in CCSv5.3.

**********************************************************************************

Then I tried to use EDMA to move data from DDR3 to DDR3.

My code was based on the EDMA examples in MCSDK and used the SYS/BIOS.

static Int32 EDMA_test (Int32 instNum, Uint8 channelNum);

In the main function, I called this sub function with this code below

EDMA_test(1,6);

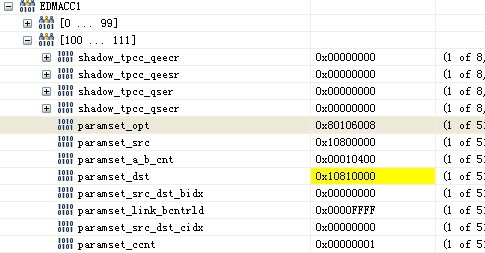

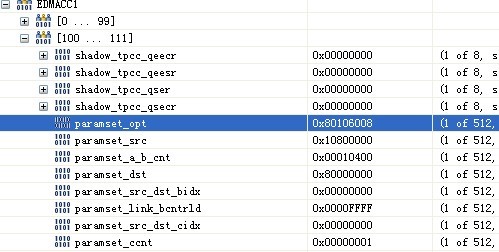

means that I used the channel 6 in EDMACC1.

The example code works on ping-pong mode. But I don't need this. So I changed the code to just move data from src to dst.

1.Firstly, I changed the src and dst addresses.

Uint16 * srcBuff1 = (Uint16 *)0x10800000;//src,L2 Uint16 * dstBuff1= (Uint16 *)0x80000000;//dst,DDR3

2. Secondly, I initialized the data in the src and dst addresses.

for (loopIndex = 0; loopIndex < 256; loopIndex++)

{

srcBuff1[loopIndex] = 0xABCD;

dstBuff1[loopIndex] = 0;

}

3. Then the code initialized the EDMA3 module, EDMA3 channel, param set and so on. This part was same as the example codes without any changes.

CSL_edma3Init(&context) hModule = CSL_edma3Open(&edmaObj, instNum, NULL, &status); chAttr.regionNum = CSL_EDMA3_REGION_GLOBAL; chAttr.chaNum = channelNum; chChannel = CSL_edma3ChannelOpen(&chObj, instNum, &chAttr, &status); CSL_edma3HwChannelSetupQue(hChannel,CSL_EDMA3_QUE_3); CSL_edma3MapDMAChannelToParamBlock (hModule, channelNum, 2); hParamPing = CSL_edma3GetParamHandle(hChannel, 2, &status);

4. After that, I modified the param set. Acnt=256, bcnt=ccnt=1 without LINK.

myParamSetup.option = CSL_EDMA3_OPT_MAKE(CSL_EDMA3_ITCCH_DIS, \

CSL_EDMA3_TCCH_DIS, \

CSL_EDMA3_ITCINT_DIS, \

CSL_EDMA3_TCINT_EN, \

0x6, CSL_EDMA3_TCC_NORMAL,\

CSL_EDMA3_FIFOWIDTH_NONE, \

CSL_EDMA3_STATIC_EN, \

CSL_EDMA3_SYNC_A, \

CSL_EDMA3_ADDRMODE_INCR, \

CSL_EDMA3_ADDRMODE_INCR );

myParamSetup.srcAddr = (Uint32)srcBuff1;

myParamSetup.aCntbCnt = CSL_EDMA3_CNT_MAKE(256,1);

myParamSetup.dstAddr = (Uint32)dstBuff1;

myParamSetup.srcDstBidx = CSL_EDMA3_BIDX_MAKE(0,0);

myParamSetup.linkBcntrld= 0xFFFF;

myParamSetup.srcDstCidx = CSL_EDMA3_CIDX_MAKE(0,0);

myParamSetup.cCnt = 1;

if (CSL_edma3ParamSetup(hParamPing,&myParamSetup) != CSL_SOK)

{

printf ("Error: EDMA Parameter Entry Setup failed\n");

return -1;

}

5. Then I enabled the transfer completion interrupt.

/* Interrupt enable (Bits 0-1) for the global region interrupts */

regionIntr.region = CSL_EDMA3_REGION_GLOBAL;

regionIntr.intr = 0x40;

regionIntr.intrh = 0x0000;

CSL_edma3HwControl(hModule,CSL_EDMA3_CMD_INTR_ENABLE,®ionIntr);

6.Triggered the EDMA manually.

CSL_edma3HwChannelControl(hChannel,CSL_EDMA3_CMD_CHANNEL_SET,NULL);

7. Finally, polled the completion interrupt bit.

regionIntr.region = CSL_EDMA3_REGION_GLOBAL;

regionIntr.intr = 0;

regionIntr.intrh = 0;

do {

CSL_edma3GetHwStatus(hModule,CSL_EDMA3_QUERY_INTRPEND,®ionIntr);

} while (!(regionIntr.intr & 0x40));

*******************************************************************

With this codes above I set the src and dst address in L2, the completion interrupt bit raises and I can find the data in the dst.

But the problem is,

When I set the src address in L2 and the dst address in DDR3, the completion interrupt bit raises but I can not find the data in the dst!!

*******************************************************************

So, can anyone one help me? I'll appreciate that!