Other Parts Discussed in Thread: OMAP3530, OMAP3503, THS8135, SN74LVC2T45

I am implemening HDMI driver on OMAP3530.

We met screen flicker and noise issue. On debug, some strange wave is founded on 'dss_hsync' and 'dss vsync'

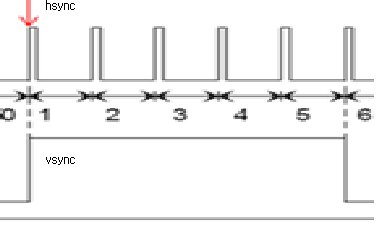

When vsync is rising, hsync is falling as the bellow figure.

C2 is dss_hsync and C1 is start of dss_vsyinc.

hsync shoud be rising edge when vsyinc is rising edge as bellows

I touched dss registers like 'DISPC_POL_FREQ', But, No change is occured. I

Is there anybody who know how to adjust this timing?