Hello. We have a problem with SPI module. We use spi_xfer() function from PDK_C6678_1_1_2_6 platfrom library:

SPI_STATUS

spi_xfer

(

uint32_t nbytes,

uint8_t* data_out,

uint8_t* data_in,

Bool terminate

)

{

uint32_t i, buf_reg;

uint8_t* tx_ptr = data_out;

uint8_t* rx_ptr = data_in;

/* Clear out any pending read data */

SPI_SPIBUF;

while( SPI_SPIBUF & CSL_SPI_SPIBUF_TXFULL_MASK ); /* Wait untill TX buffer is not full */

for (i = 0; i < nbytes; i++)

{

//// while( SPI_SPIBUF & CSL_SPI_SPIBUF_TXFULL_MASK ); /* Wait untill TX buffer is not full */

/* Set the TX data to SPIDAT1 */

data1_reg_val &= ~0xFFFF;

if(tx_ptr)

{

data1_reg_val |= *tx_ptr & 0xFF;

tx_ptr++;

}

else

data1_reg_val = (data1_reg_val & 0xFFFF0000) | (buf_reg & 0xFF);

/* Write to SPIDAT1 */

if((i == (nbytes -1)) && (terminate))

{

/* Release the CS at the end of the transfer when terminate flag is TRUE */

SPI_SPIDAT1 = data1_reg_val & ~(CSL_SPI_SPIDAT1_CSHOLD_ENABLE << CSL_SPI_SPIDAT1_CSHOLD_SHIFT);

} else

{

SPI_SPIDAT1 = data1_reg_val;

}

/* Read SPIBUF, wait untill the RX buffer is not empty */

while ( SPI_SPIBUF & ( CSL_SPI_SPIBUF_RXEMPTY_MASK ) );

/* Read one byte data */

buf_reg = SPI_SPIBUF;

if(rx_ptr)

{

*rx_ptr = buf_reg & 0xFF;

rx_ptr++;

}

}

return SPI_EOK;

}

CPU core operates on freq = 1000 MHz. So SPI module clock = Sysclk7 = CPU clock / 6 = 167 MHz. SPI register settings are:

SPI_DAT1 = 0x10010000;

SPI_DELAY = 0x0;

SPI_FMT0 = 0x00010308;

SPI output clock = 167 / (3+1) = 41,7 MHz.

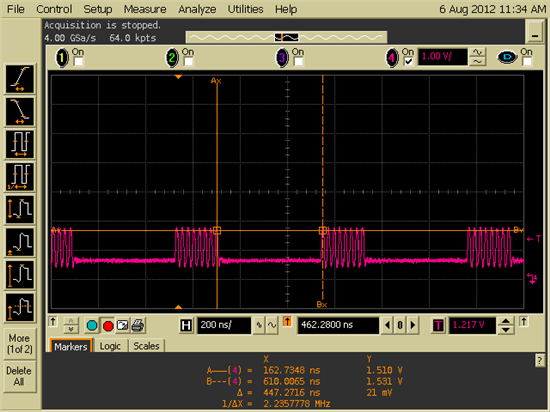

With these settings we have behavior shown on the figure (only SPI output clock is shown):

The problem is: a lot of time between transactions - approx. 450-500 nS.

The only place in program where it can "idle" a lot of time is:

while ( SPI_SPIBUF & ( CSL_SPI_SPIBUF_RXEMPTY_MASK ) );

So, the question is: why this flag does not clear so long?

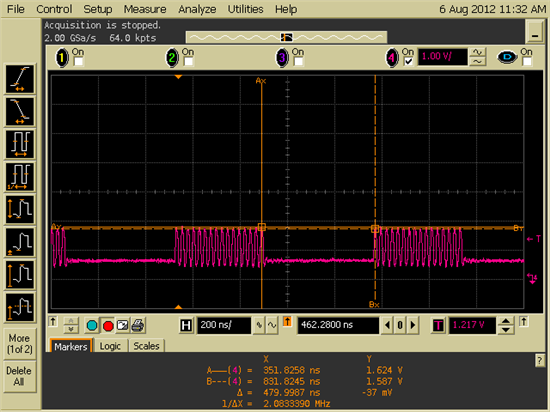

P.S. With 16-bits mode transactions behavior is the same: