Hello,

First Question:

We have the DM355 and I have output from our MT9V032 (752x480 VGA) camera. :-) But, the way I obtained video is by:

Working: CCDC -> RAW to SDRAM -> Ipipe IF -> Ipipe -> YUV422 to SDRAM -> OSD Video Window -> LCD Screen

Not working/Desired: CCDC -> IpipeIF -> Ipipe -> YUV422 to SDRAM -> OSD Video Window -> LCD Screen

Basically, I want the CCDC to not have to write RAW data to SDRAM. I believe this is unnecessary and another "jump"/"layover" not needed. Whenever I set the iPipeIF.CFG register INPSCR to select data input to 0-CCD Controller (instead of 1-From SDRAM (raw data)), all l get a big gray "choppy" screen (which is sensitive to CCDC input light/dark). But it is all gray and I see no major output.

Question:

1) What else needs to be taken into consideration when you change the IpipeIF from SDRAM Raw to CCDC direct input? I don't understand what else would need modification.

2) Is there any example code of routing data from the CCDC directly to the ipipe? I am currently using the example:

~/dvsdk_2_00_00_22/PSP_02_00_00_140/examples/dm355/ipipe/

ipipe_config.c, etc...

3) Will direct data from the CCDC to the iPipe fix this issue?

Second Question:

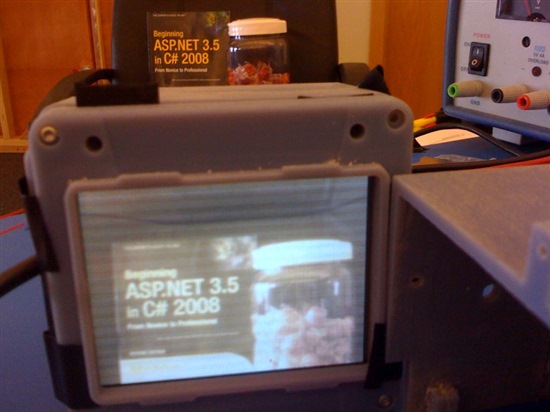

My output in the "working" case looks like there is "wavy" lines throughout. I am more than willing to give you all my registers and give as much detail as I can about the sensor. We had to sign a NDA for details, but basic info I believe I can share.

Question:

1) What registers/considerations should be looked at to try to fix the "overscanning"/"wavy" lines?? The picture below is a pretty good representation of what is happening.

Please see the picture attached: