The minimum timing requirement for EM_WAIT pulse duration is 2 EMA_CLK period.

When EM_WAIT is less than 2 EMA_CLK period, may the Extended Wait be performed?

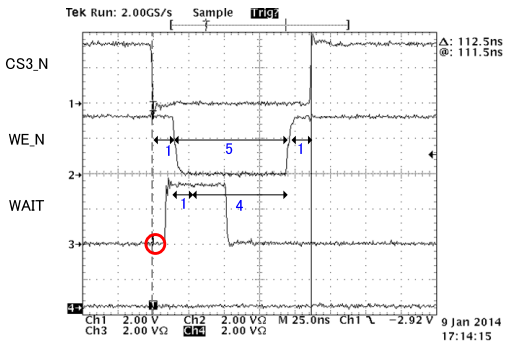

Our customer traced the Asynchronous Memory Write Timing with Extended Wait Mode. It as follows:

EMA_CLK clock frequency: 62.5MHz (16nsec)

CE3CFG.W_SETUP:1 EMA_CLK period

CE3CFG.W_STROBE:4 EMA_CLK period

CE3CFG.W_HOLD:1 EMA_CLK period

AWCC.CS3_WAIT:01b (EMA_WAIT[1] pin is used)

AWCC.WP1: 0b (EMA_WAIT[1] pin is low)

AWCC.MAX_EXT_WAIT: 80h

The strobe period is expanded to 5 EMA_CLK period. While EMA_CS3 is asserted, the duration of asserted EM_WAIT is less than 2 EMA_CLK period.

Best regards,

Daisuke