Other Parts Discussed in Thread: AM3357, SYSBIOS

Hi,

We use the GPMC module in the AM3357 accessing an asynchronous Dual Port RAM (16Bit databus).

We write three values as you can see below:

//### Test

*((volatile unsigned short *)(0x09000004))=0x0001;

*((volatile unsigned short *)(0x09000006))=0x0002;

*((volatile unsigned short *)(0x09000008))=0x0003;

//asm(" DMB");

//### Test Ende

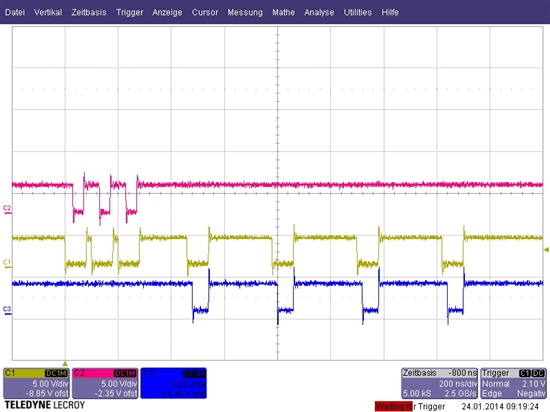

The writes itself work as it should. If we watch the signals on an oscilloscope we see that the chip select signals goes low for 8 times and only for the expected 3 times the WEn signal goes low. We would expect the chip select signal to go low only 3 times.

If I change the code to the following...

//### Test

*((volatile unsigned short *)(0x09000004))=0x0001;

asm(" DMB");

*((volatile unsigned short *)(0x09000006))=0x0002;

asm(" DMB");

*((volatile unsigned short *)(0x09000008))=0x0003;

asm(" DMB");

//### Test Ende

...I can see the expected number of low cycles of the chip select signal.

Does anyone from TI has an idea why this happens? Is this a bug within the GPMC module?

Thanks and best regards,

Patrick