Other Parts Discussed in Thread: AM3352

hi,TI team,

I need to support a STN LCD with AM3352.the LCD resolution is 320*240.

but the image showed in LCD is

line 239

line 0

line 1

...

line 238

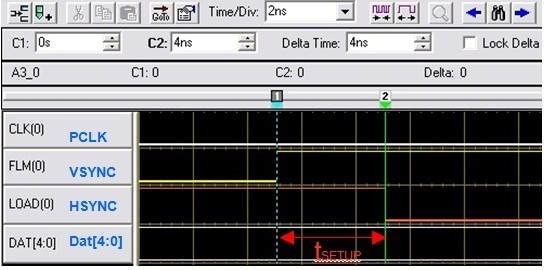

I try to change the vsync timing to adjust it ,but it has no effect.

the lcd controller register value:

Revision ............... 4f201000

Control ................ 0000bb01

Status ................. 00000000

Raster Control ......... 00080203

Raster Timing 0 ........ 01010670

Raster Timing 1 ........ 010104ef

Raster Timing 2 ........ 00000000

Subpanel Display 1 ..... 00000000

Subpanel Display 2 ..... 00000000

DMA Control ............ 00000641

Frame Buffer 0 Base .... 8e900000

Frame Buffer 0 Ceiling . 8e904b1c

Frame Buffer 1 Base .... 8e900000

Frame Buffer 1 Ceiling . 8e904b1c

the vbp = 1,vsw = 1,vfp = 1