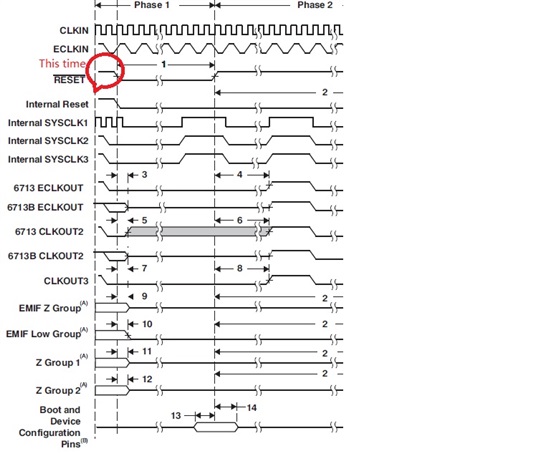

I would like to confirm what state of the 6713 GPIO between powerup and negedge of reset.

According to Reset Timing of Data manual, Notes B(Boot and Device Configuration Pins),The state of these pins is Tri-State, others is Uncertain state at these time. Is Understanding OK ?

Can someone tell me what state of two group GPIO between powerup and negedge of reset, tri-state/input /output or uncertain state? Thank you very much!