We are using a DM648 DSP connected to a P1022 powerpc (via the HPI). Due to a lack of chip-select pins, we generate the chip-select signal for the DSP in a Xilinx CPLD. When we continuously read from the data register with auto-increment, the address is sometimes (about every 3000000 accesses) incremented twice. So it seems that the DSP recognizes two read accesses instead of one. We analyzed the bus communication on the protocol level and could not find any unintended DSP access or any other protocol violations.

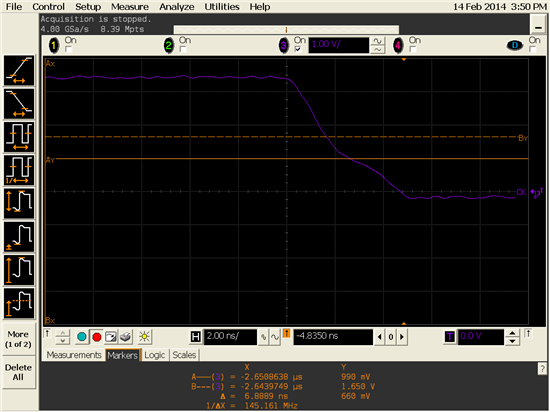

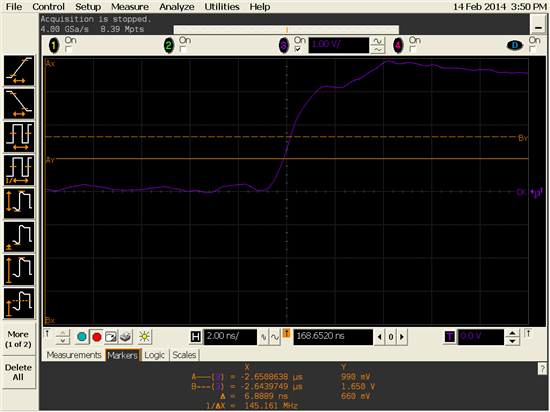

Eventually we discovered a correlation of the error with the slew rate of the chip select signal (Which is connected to HDS1 & HCS, HDS2 is connected to 3V3). By increasing the gradient of the chip select signal, the occurrence rate of the error can be reduced. Our assumption is now that the slew rate provided by the CPLD is too slow for the DSP. In an older system with the same DSP we do not have any problem and in this case the chip select signal is provided by the powerpc directly - with a steeper slew rate!

Is there anywhere a requirement for the steepness of the edges of the chip select signal? I could only find transition time requirements for the clock inputs of the DSP.

Thank you and best regards,

Peter Brunmayr