Hi,

I am now using EVM8168 for developing. I managed to generate some dummy 1080p60 BT.1120 video frame by FPGA and send these dummy frame into DM8168 via VIN0.

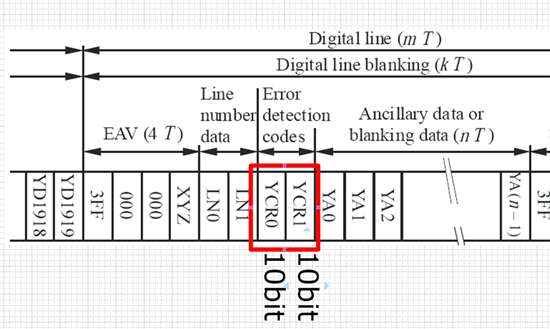

When dealing with the FPGA HDL, I was confused by the CRC code. Because of the 20bit BT.1120 standard, the polynomial generator equation is definded as below:

EDC(x) = x^18 + x^5 + x^4 + 1;

That means, a 20-bit CRC code would be generated and recorded in the Error detection code

However, the DM8168 only supports 16bit-BT.1120 VIN port mode, which indicates that we should leave the last 2 bits (2 LSB) out. I am not sure whether the CRC mechanism would work, when we tried to transfer BT.1120 data with a truncated-16bit CRC code.

Could you please tell me how a 16bit-truncated CRC code would be work in our DM8168 system?

Thank you!

Naroah

Feb/24/2014