Hello people,

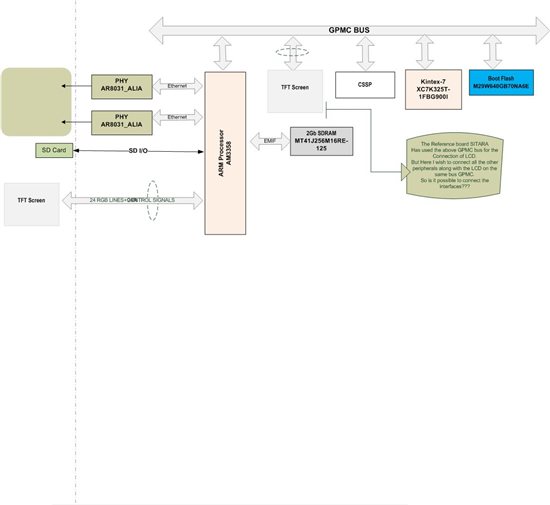

I am trying to design a board with the use of AM3358 processor. Here the processor is connected to various other external peripherals. It is also connected to the FPGA (Kintex 7). The processor and the FPGA has GPMC bus in common, to communicate between the two.

Not as per sitara (starter kit) reference board, they have not used boot flash, also the schematic shows that the GPMC bus is not used by them for booting purpose but instead they have used it for connecting LCD on to the bus.

Now My question is that "if at all, I keep the LCD and RGMII2 connections as per the SITARA board, then is it possible for me to connect the remaining peripherals to ARM AM3358 using the same bus as shown in the diagram below? "

If yes how can I use it?

As per the PIN MUX tool provided by TI, it shows that IO's conflict when I chose the two inerfaces to be connected i.e. GPMC as well as LCD. Is there a solution to this problem?

Thank you in advance.

Waiting for reply.

Regards

Parth Bapaye