Hi Champs,

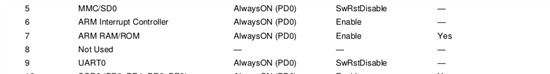

I'm trying to disable the OMAP-L138 ARM RAM/ROM module(LPSC #7) in PSC0, its default state is enable.

But I can not make it disable by following a state transition procedure described in TRM SPRUH77A page-187.

I've done it on DSP side, though.

So, could you please let me know how I can disable the module?

Thanks in advance for your cooperation.

Best regards,

j-breeze

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.