Dear sir,

In the DVRRDK-04.01.00.02 u-boot, I set VENC and VideoPLL values as below

For 1080p:

/** HD_VENC_D_VOUT1 **/

configVenc(0x6000, 0x2, argv[0], 1920, 88, 148, 44, 1080, 4, 36, 5);

/** HD_VENC_A **/

configVenc(0x8000, 0x0, argv[0], 1920, 88, 148, 44, 1080, 4, 36, 5);

/** HD_VENC_D_VOUT0 (DVO2) **/

configVenc(0xA000, 0x1, argv[0], 1920, 88, 148, 44, 1080, 4, 36, 5);

WR_MEM_32(CM_CLKOUT_CTRL, 0x0);

VideoPLL(0x6E, 0x2, 0xD, 0xC00000, 0x4, 0xA, 0x0, 0x8, 0xA, 0x0, 0x8, 0x0, 0x0);

For 720p:

/** HD_VENC_D_VOUT1 **/

configVenc(0x6000, 0x2, argv[0], 1280, 110, 220, 40, 720, 5, 20, 5);

/** HD_VENC_A **/

configVenc(0x8000, 0x0, argv[0], 1280, 110, 220, 40, 720, 5, 20, 5);

/** HD_VENC_D_VOUT0 (DVO2) **/

configVenc(0xA000, 0x1, argv[0], 1280, 110, 220, 40, 720, 5, 20, 5);

WR_MEM_32(CM_CLKOUT_CTRL, 0x0);

VideoPLL(0x6E, 0x2, 0xD, 0xC00000, 0x4, 0xA, 0x0, 0x10, 0xA, 0x0, 0x10, 0x0, 0x0);

Load 1920*1080 (for 1080p) and 1280*720 (for 720p) bmp 24bits to display.

Q1: For 1080p, the screen shoule flash, but 720p don't.

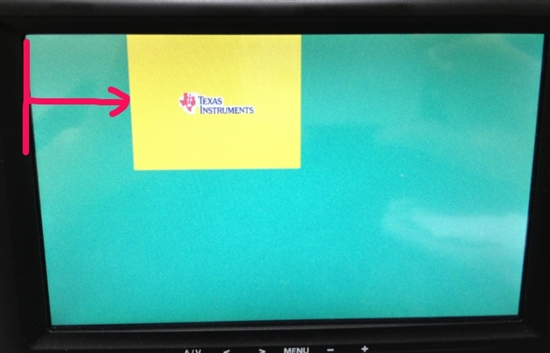

Q2: For 1080p & 720p, the image show at screen, the image is shift at Horizontal or Vertical.

How to slove the flash and shift issue?