hi,everyone

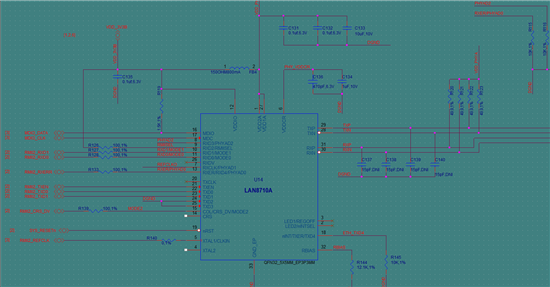

I use a LAN8710A PHY connect am3359 through RMII2 ,I used the SDK06.00.00 is latest version,

I adjust the configuration in uboot and provide a external low jitter 50 MHz RMII LVCMOS reference clock to both LAN8710a and AM335x.

First I configure the gmii_sel register is 0x75,then configure the pinmux

static struct module_pin_mux rmii2_pin_mux[] = {

{OFFSET(gpmc_a11), MODE(3) | RXACTIVE}, /* RMII2_RXD0 */

{OFFSET(gpmc_a10), MODE(3) | RXACTIVE}, /* RMII2_RXD1 */

{OFFSET(gpmc_wpn), MODE(3) | RXACTIVE}, /* RMII2_RXERR */

{OFFSET(gpmc_a0), MODE(3)}, /* RMII2_TXEN */

{OFFSET(gpmc_a5), MODE(3)}, /* RMII2_TXD0 */

{OFFSET(gpmc_a4), MODE(3)}, /* RMII2_TXD1 */

{OFFSET(gpmc_wait0), MODE(3) | RXACTIVE}, /* RMII2_CRS_DV */

{OFFSET(mii_col), MODE(1)}, /* RMII2_REFCLK */

{OFFSET(mdio_data), MODE(0) | RXACTIVE | PULLUP_EN},/* MDIO_DATA */

{OFFSET(mdio_clk), MODE(0) | PULLUP_EN}, /* MDIO_CLK */

{-1},

};

I pulldown the PHY address pin,configure the phy_id like this

static struct cpsw_slave_data cpsw_slaves[] = {

{

.slave_reg_ofs = 0x208,

.sliver_reg_ofs = 0xd80,

.phy_id = 1,

},

{

.slave_reg_ofs = 0x308,

.sliver_reg_ofs = 0xdc0,

.phy_id = 0,

},

};

then I execution dhcp in uboot ,it appears that

U-Boot# dhcp

link up on port 0, speed 100, full duplex

BOOTP broadcast 1

BOOTP broadcast 2

BOOTP broadcast 3

BOOTP broadcast 4

BOOTP broadcast 5

BOOTP broadcast 6

BOOTP broadcast 7

BOOTP broadcast 8

BOOTP broadcast 9

BOOTP broadcast 10

Retry count exceeded; starting again

using musb-hdrc, OUT ep1out IN ep1in STATUS ep2in

MAC bc:6a:29:73:f6:90

HOST MAC de:ad:be:af:00:00

RNDIS ready

ERROR: The remote end did not respond in time.

at ether.c:2395/usb_eth_init()

link up on port 0, speed 100, full duplex

Did I miss a configuration step?Is there anything else that configure RMII2?