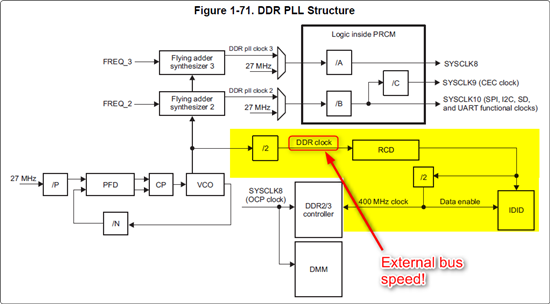

1.) Sysclk 8 derived from the DDR PLL is very confusing in the specification. Looking at Figure 1-71 it appears the sysclk8(OCP clock) should be configured for VCO/(MDIV1 * 2). Is this correct?

a. 1333MT/S (666 MHz), sysclk8=333Mhz.

b. 1600 MT/S (796.5 MHz), sysclk8=398.200 MHz

2.) In SPRS614E – Table 8-15 SysClk8 Frequencies seems to indicate that I need a TI8168 Device Speed rating of 4 in order to achieve a 1600 MT/S DDR3 given Sysclk8 only allows 380 MHz for blank and 2. However, this table is suspect, since I believe sysclk8 max is 400 Mhz not 450 Mhz.

Please advise.

Thanks,

Mark