Hello everyone,

I'm testing SRIO on C6678, the plateforme i'm using contains three Dsps (C6678)

connected to each other using a switch.

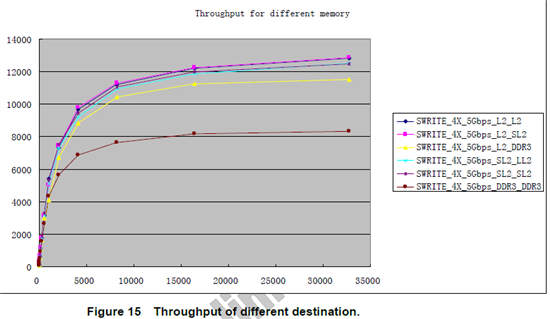

I test the troughput using configuration of 4x and sending transactions swrite at 5Gbps and then i change every time memories where i write and from where i send data .

but My question is : During the test i sent from differents memories and i noticed that i got the same result presented in the TI document "Srio_Programming_Performance" on page 43 ,

but i can't found the explaination why does the transactions comming from L2 have the best speed unlike those comming from MSM and DDR ??

if someone can answer my question to clarify this aspect I would be very grateful.

thank you ,waitting for your answer!

Regards ,

Asma