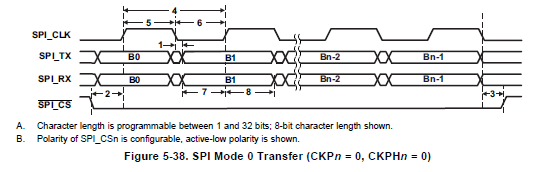

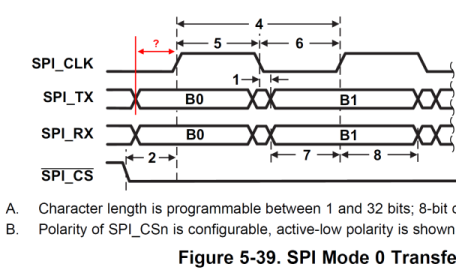

Hello, looking at figure 5-38 from the C5505 datasheet, when operating in SPI mode 0, is there a specification that indicates when SPI_TX data becomes valid with respect to the first rising clock edge (sampling of bit B0 in the diagram)? This is needed to guarantee the RX setup time of the connected device.

Thanks - AM