hi

in the project qmssIpcBenchmark

System_printf ("Core %d : L1D cache size %d. L2 cache size %d.\n", coreNum, CACHE_getL1DSize(), CACHE_getL2Size());

System_printf ("address of monolithicDesc[] = 0x%x. Converted=0x%x\n", monolithicDesc, l2_global_address ((UInt32) monolithicDesc));

the log is:

Core 0 : L1D cache size 4. L2 cache size 0.

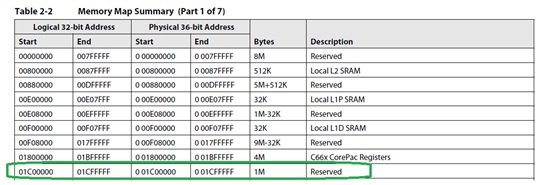

address of monolithicDesc[] = 0xc100000. Converted=0x1c100000

1.i want to know the log:cache size 4,what is its meaning?

2.the address of monolithicDesc[] = 0xc100000 ,it is in the shared memory,why it is mapped to 0x1c100000,the address is a reserved in 6678 memory map.