Other Parts Discussed in Thread: OMAP-L138, AM1808, OMAPL138

Hi,

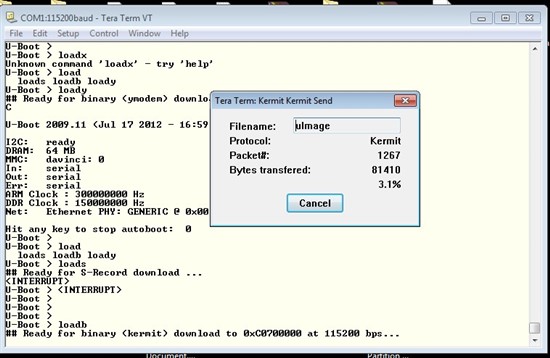

I downloaded kernel image into DDR2 at address 0xC0700000 with Ymodem exchange proposed by UBOOT (loady command).

But when I execute "bootm 0xC0700000", kernel is not launched.

----------------------------------------------------------------------------------------------

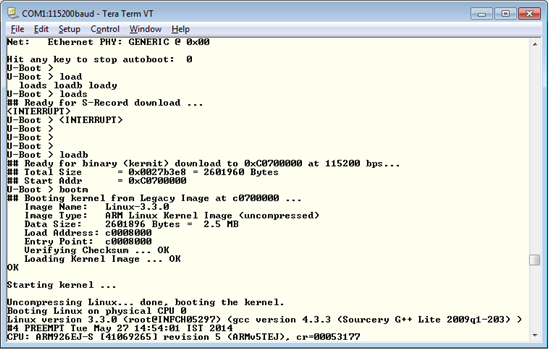

U-Boot > bootm 0xc0700000

## Booting kernel from Legacy Image at c0700000 ...

Image Name: Linux-3.3.0

Image Type: ARM Linux Kernel Image (uncompressed)

Data Size: 2397792 Bytes = 2.3 MiB

Load Address: c0008000

Entry Point: c0008000

Verifying Checksum ... Bad Data CRC

ERROR: can't get kernel image!

U-Boot >

----------------------------------------------------------------------------------------------

It's a problem of download? or kernel image?

Thanks

Best Regards

Sebastien