hi, all

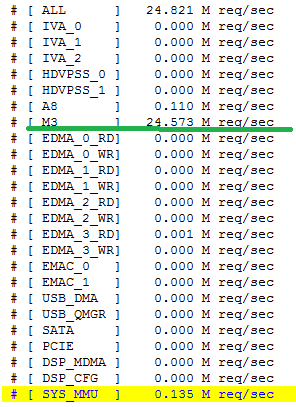

after DM8168 being load ok, we use mem_stats.out tools to show memory usage, and we get:

it seem that M3 consume too much bandwidth. we do the following test to find the reason:

a) Is the video-m3/vpss-m3's code/data/stack cacheable ?

[result]: we check the AMMU_m3.cfg, it already configure cacheable;

b) we force set the video-m3/vpss-m3 in exceptions (by read memory address: 0xffff0000)

[result]: M3 req/sec reduce to 0;

c) FAE told us maybe the idle task doing something, then we execute following code sequence:

Task_disable();

for (i = 0; i < 16; i++)

{

Hwi_disableInterrupt(i);

}

while (1);

[result]: the M3 req/sec reduce to 0;

[summarize]: it seem the some code's raise the problem, can anyone give some tip ? thanks.