Hello,

I'm using TMDSEVM6657LS in a Blue-Ema uTCA chasis with a Nat-MCH-PCIE-GEN3,when i plug the EVM board to the slot which is used for RootComplex it can be identified by mch, but when i use mch's command to see the ekey status,it only have Ethernet's output.

when i plug EVM to any other slot which is for downstream,Ethernet and PCIE status can be printed .

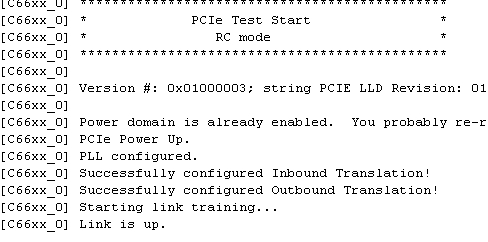

I already have SW5.3 off to have backplane clock. and download the PCIE-example project to the dsp ,and set PCIE mode to RC. I only use ccs5to debug with xbs200 emulator,i guess that means i successfully download the code to DSP.

Do I miss something that will cause that problem?

Regards,

athrun