Hi all,

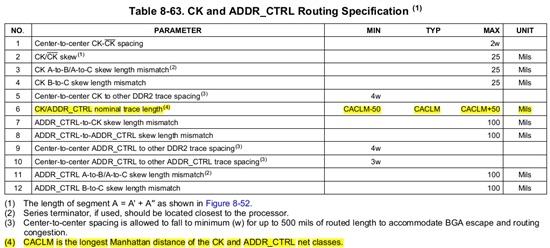

I checked the DM8148 datasheet as follows portion. My query was CACLM only represented the distance of CPU to latest one DDR. That did not comprise the total length. The total length mean from CPU to all DDRs(4x 8bit or 2x 16bit per controller) trace. Was my view right?

B.R.

OC