Hi all,

When I read the DDR3 Design Requirements for KeyStone Devices(SPRABI1B), I am confused about some details.

So I want to show my understanding about these and ask you help me to confirm whether my understanding is right or not.

**************************************************************************************************

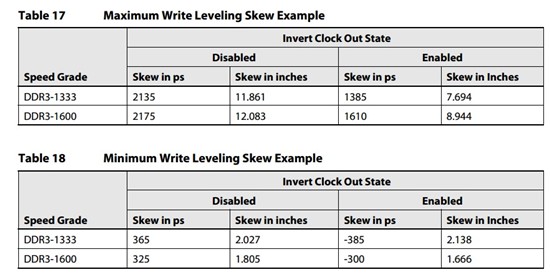

From what I understood, according to this pic below

(1) when the Invert clock out state is disabled and DDR3 runs at 1333MT/s

2.027 inchs < addr/cmd/ctl length - data length < 11.861

(2) when the Invert clock out state is enabled and DDR3 runs at 1333MT/s

-2.138 inchs < addr/cmd/ctl length - data length < 7.694

Am I right?

If it is true, I think this constraint is too generous when the Invert clock out state is enabled!

**************************************************************************************************

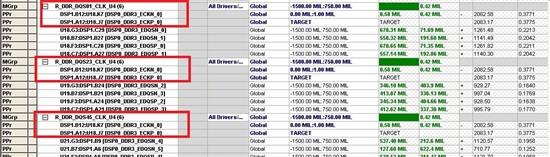

In the C6670 EVM board, the layout engineer sets the constraint about the skew between addr/cmd/ctl length and data length showed in the pic below

the U18 is the first DRAM on the fly-by topology and the others are U19, U21,U22.

From what I understand, to a given DRAM, the skews between the CLK length to it and the DQS length to it should be concerned.

But why constrain the skews between the CLK length to the first DRAM and the DQS length to every DRAM according to the pic above?

**************************************************************************************************

That's my question. Hope anyone help me.

Regards,

Feng