请原谅我在E2E社区来发中文帖子,主要是英文水平太差,估计用英文写出来大家更看不明白了。闲话不多说,进入正题。

我们公司最近一个项目做了一个C6670多核DSP的一个板子。板子和6670EVM板的区别是,没有接I2C EEPROM,DDR存储器是由2片MT41J64M16JT-15EIT(速度1333MHz)组成32位的存储器,DDR参考时钟是66.67MHz。spi nor flash用的是N25Q128A11ESE40F,连接的是CS0。

最近在做core0单核boot的时候发现,板子上配置的是从spi启动模式(代码烧写完成之后,DSP的GPIO15~GPIO0的设置是0001 0100 0000 1101)。如果在生成烧写image的时候,image文件中不添加DDR configuration table部分,该板子可以成功boot,如果在image文件中添加DDR configuration table部分,该板子就不能成功boot,而且此时连上仿真器去查看相应的内存,发现bootloader只是将flash中的boot parameter table部分的数据搬移到L2,其他字段的数据均没有搬移。生成烧写image文件的工具链是在中文社区里面的http://www.deyisupport.com/question_answer/dsp_arm/c6000_multicore/f/53/t/8065.aspx下载的1423.spi_boot_suit_v2.3.1_release.zip。

接下来,我又在http://e2e.ti.com/support/dsp/c6000_multi-core_dsps/f/639/p/288354/1006025.aspx#1006025找了个例程7080.SPIboot_ddr.zip。在它的基础上我作了一些修改,就是在程序代码里面将DDR configuration table的结构体BOOT_EMIF4_TBL_T作为一个数据段,在cmd文件里将它链接到DDR configuration table被搬移后的存储空间。将编译转换成烧写image文件然后下载到我们的板子上,能成功将DDR config table搬移到0x8f3500上去,但是配置出来的结果是不能正常访问DDR,问题出在RBL没有正确将DDR PLL CTL0配置正确,我在DDR config table设置的pllMult是19,但是RBL配置出来的是18,所以导致DDR不能正常工作(我的主程序中有DDR测试并将测试结果通过GPIO告知FPGA)。根据这一结果,我以为RBL会把DDR configuration table中设置的pllMult减去1再写进去,然后我将pllMult改成20之后再下载到板子上,结果又跟以前一样,RBL只搬移了boot parameter table,其他数据都没搬移,而且很奇怪的是只要我更改DDR config table任意一个数据,下载之后度会出现只搬移boot parameter table的现象。请问造成这种结果的原因是什么???

我现在将我工程中的DDR configuration table的结构体BOOT_EMIF4_TBL_T代码、链接文件和相关寄存器的截图附后,附件中有个转后的镜像文件i2crom.ccs。请你帮我们分析一下,同时给我们下一步实验提出你们的宝贵意见和建议。谢谢!!!

根据DDR3 Register Calc v4算出来的寄存器配置结果是:

|

SDRAM Register |

Address |

Value (hex) |

|

DDR_SDTIM1 |

0x21000018 |

1113783C |

|

DDR_SDTIM2 |

0x21000020 |

304F7FE3 |

|

DDR_SDTIM3 |

0x21000028 |

559F849F |

|

DDR_SDCFG |

0x21000008 |

63066A32 |

|

DDR_SDRFC |

0x21000010 |

00001458 |

BOOT_EMIF4_TBL具体代码如下:

#include "tiboot_c66x.h"

#pragma DATA_SECTION (emif4Cfg, ".emif4Cfg")

const BOOT_EMIF4_TBL_T emif4Cfg =

{

BOOT_EMIF4_ENABLE_pllCtl | \

BOOT_EMIF4_ENABLE_sdRamConfig | \

BOOT_EMIF4_ENABLE_sdRamRefreshCtl | \

BOOT_EMIF4_ENABLE_sdRamTiming1 | \

BOOT_EMIF4_ENABLE_sdRamTiming2 | \

BOOT_EMIF4_ENABLE_sdRamTiming3 | \

BOOT_EMIF4_ENABLE_ddrPhyCtl1 | \

BOOT_EMIF4_ENABLE_sdRamOutImpdedCalCfg,

0, //pllPrediv

19, //pllMult

0, //pllPostDiv

0x63066A32, // sdRamConfig

0, // UINT32 sdRamConfig2;

0x00001450, // UINT32 sdRamRefreshCtl;

0x1113783C, // UINT32 sdRamTiming1;

0x304F7FE3, // UINT32 sdRamTiming2;

0x559F849F, // UINT32 sdRamTiming3;

0, // UINT32 lpDdrNvmTiming;

0, // UINT32 powerManageCtl;

0, // UINT32 iODFTTestLogic;

0, // UINT32 performCountCfg;

0, // UINT32 performCountMstRegSel;

0, // UINT32 readIdleCtl;

0, // UINT32 sysVbusmIntEnSet;

0x70073214, // UINT32 sdRamOutImpdedCalCfg;

0, // UINT32 tempAlterCfg;

0x0010010F, // UINT32 ddrPhyCtl1;

0, // UINT32 ddrPhyCtl2;

0, // UINT32 priClassSvceMap;

0, // UINT32 mstId2ClsSvce1Map;

0, // UINT32 mstId2ClsSvce2Map;

0, // UINT32 eccCtl;

0, // UINT32 eccRange1;

0, // UINT32 eccRange2;

0x305 // UINT32 rdWrtExcThresh;

};

CMD链接文件内容如下:

-c

-a

-stack 0x1000

-heap 0x400

MEMORY

{

DDR_CFG : o = 0x108f3500, l = 0x100

L2MAGIC : o = 0x108ffffc, l = 0x4

BOOT_CORE0 : o = 0x10800000, l = 0x000000c0

L2 : o = 0x108000C0, l = 0x000f2d00

DDR3_CODE : o = 0x80000000, l = 0x01000000

DDR3_DATA : o = 0x81000000, l = 0x0f000000

}

SECTIONS

{

.emif4Cfg > DDR_CFG

.lmagic > L2MAGIC

.stack > L2

.far > L2

.text > L2

.const > L2

.cinit > L2

.bss > L2

.cio > L2

.neardata > L2

.switch > L2

.sysmem > L2

platform_lib > L2

.fardata > L2

}

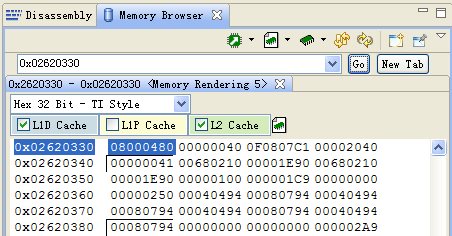

正常程序初始化DDR之后的与DDR相关的寄存器:

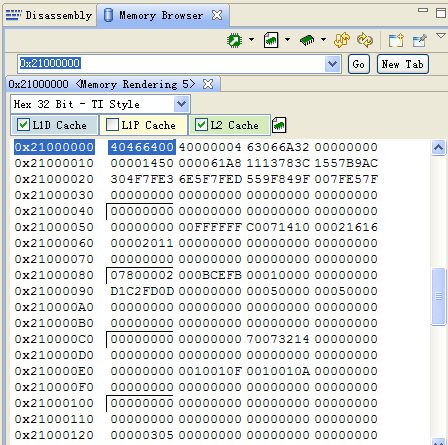

RBL加载初始化之后的与DDR相关的寄存器:

转后的镜像文件i2crom.ccs