I would need to perform 17 dma channel transfers with their respective 34 link and 34 chain channel settings.

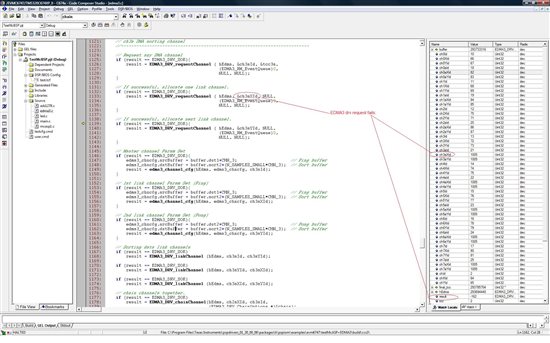

After requesting the 24th channel for link, EDMA3_DRV_requestChannel function returns -162

What could be wrong whit this? I use C6747 platform and edma3_lld_01_11_00_03 version

Thanks in advance,

Gaston