We have a legacy DSP board that uses a bunch of TI TMS320C 6202 GJL chips. Each DSP has two 16-bit SDRAMs attached to it.

This board has been shipping for nearly 10 years now, and the SDRAM we use is going EOL.

We currently use an ISSI 42S16100C1. This is a 512K Words x 16 Bits x 2 Banks SDRAM (16 Mb).

We replaced a board with the new rev of the ISSI part - IS42S16100E (same memory arrangement and density).

After we replaced some old parts with new ones on a board, the board stopped working - has data errors.

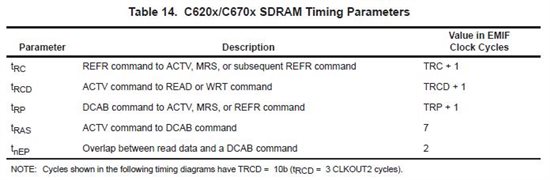

I found that there are 7 registers in the chip for the EMIF interface for the 6202 (page 27 of the " TMS320C6000 EMIF-to-External SDRAM Interface" application note SPRA433E - September 2007). We currently configure these as follows:

GBLCTL = 0x0000 3040

CE1CTL - N/A, we use CE2 for both SDRAMs

CE0CTL - N/A, we use CE2 for both SDRAMs

CE2CTL - 0x0000 0030

CE3CTL - N/A, we use CE2 for both SDRAMs

SDCTL = 0x0732 A000

DTIM = 0x0000 1F40

This means that for SDRAM Control:

-TRC = 10d

-TRP = 2d

-TRCD = 3d

-SWID = 1 (not sure if this is correct)

And for SDRAM Timing:

-Counter = 1d

-Period = 3904d

For the DRAM Timing parameters:

OLD rev C1 NEW rev E

TRC 54 ns 54 ns

TRP 18 ns 18 ns

TRCD 16 ns 18 ns