Hello,

I am using 66AK2H12/06 USB3.0 interface.

There is no detail FLADJ_30MHz field in FLADJ register.

And, its register is defferent from xHCS standard by Intel.

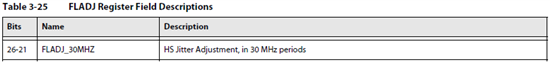

66AK2H : FLADJ (Jitter adjustment and other pseudo-static parameters)

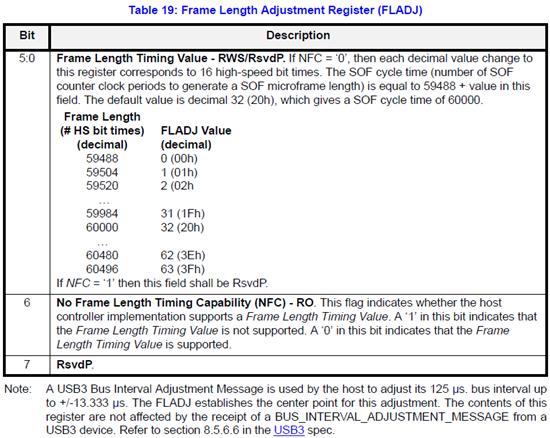

xHCI standard : FLADJ (Frame Length Adjustment Register)

You can see detail of the xHCI standard

http://www.intel.com/content/dam/www/public/us/en/documents/technical-specifications/extensible-host-controler-interface-usb-xhci.pdf

(P280) 5.2.4 Frame Length Adjustment Register (FLADJ)

Question:

Could you let me know about detail of FLADJ_30MHz ?

Can I have any documentation or article of it(FLADJ_30MHz)?

Best regards, RY

spruhj7 (P97) 3.1.24 FLADJ [Offset = 0x0704]