Hi,

I have DM8127 EVM module. I am trying to initialize DDR3 and U-Boot using CCS, as described in below link.

http://processors.wiki.ti.com/index.php/TI814x-DDR3-Init-U-Boot_Wordwise_SWleveling

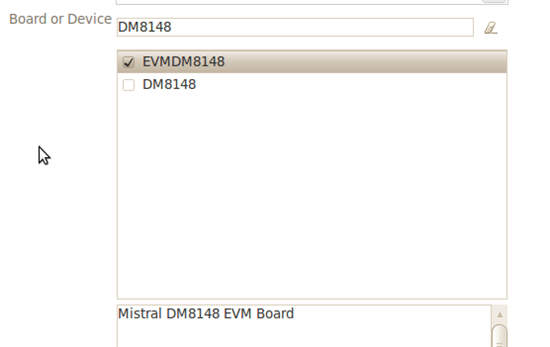

I have Spectrum Digital's XDS510 USB emulator. While creating target configuration I have selected,

Connection = TI XDS510 USB Emulator

Board or Device = TI814x(no STM, ETB only)

Now, when I try to load DDR3_slave_ratio_search_TI814x.out file, it shows me an error that,

Can't Run Target CPU:

Error 0x80001820/-1141

Fatal Error during: Execution, Timeout, Target,

Processor communication timeout.

It is recommended to RESET EMULATOR. This will disconnect each target,

perform an emulation reset, and then reconnect each target.

Power cycle the target board before continuing.

Error message on console,

CortexA8: Breakpoint Manager: Retrying with a AET breakpoint

CortexA8: Warning: Error 0x40000108/-1169 Warning during: Break Point, Cache, Error during instruction cache flush

CortexA8: Breakpoint Manager: Retrying with a AET breakpoint

CortexA8: Warning: Error 0x40000108/-1169 Warning during: Break Point, Cache, Error during instruction cache flush

Any help would be highly appreciated.

Regards,

Krinali Shah