Now i try to develop a simple PCIe device.

I read below code and document.

C:\ti\mcsdk_2_01_02_06\tools\boot_loader\ibl\src\device\c665x\c665xinit.c - void iblPCIeWorkaround()

and

PCIe Use Cases for KeyStone Devices (SPRABK8—December 2011) - 5 PCIe Programming Example

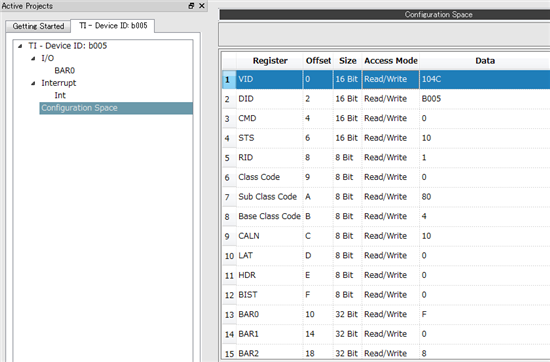

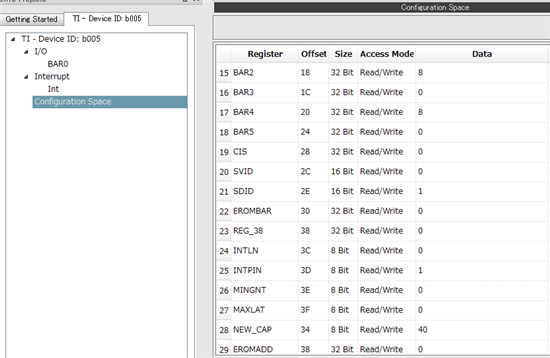

My device detected by Windows 7 PC as Multimedia Controller.

But BAR0,1 is unexpected.

In C6657, I set 0x00000000 to BAR0 (0x1010). My device can't be detected by Windows PC.

In Windows PC, I set 0x70000000 to BAR0 (0x1010). Read value is not same to value at 0x00800000.

Are there any parameters that are wrong ?

Or Procedure is wrong?

void main (void)

{

uint32 i;

uint32 reg;

memset (&iblStatus, 0, sizeof(iblStatus_t));

iblStatus.iblMagic = ibl_MAGIC_VALUE;

iblStatus.iblVersion = ibl_VERSION;

iblStatus.activeDevice = ibl_ACTIVE_DEVICE_I2C;

ibl.iblMagic = 0xCEC11EBC;

ibl.pllConfig[ibl_MAIN_PLL].doEnable = TRUE;

ibl.pllConfig[ibl_MAIN_PLL].prediv = 1;

ibl.pllConfig[ibl_MAIN_PLL].mult = 20;

ibl.pllConfig[ibl_MAIN_PLL].postdiv = 2;

ibl.pllConfig[ibl_MAIN_PLL].pllOutFreqMhz = 1000;

// ibl.pllConfig[ibl_DDR_PLL].doEnable = TRUE;

// ibl.pllConfig[ibl_DDR_PLL].prediv = 3;

// ibl.pllConfig[ibl_DDR_PLL].mult = 40;

// ibl.pllConfig[ibl_DDR_PLL].postdiv = 2;

// ibl.pllConfig[ibl_DDR_PLL].pllOutFreqMhz = 1333;

/* Pll configuration is device specific */

devicePllConfig ();

#define L1PEDCMD 0x01846408

#define L2EDCEN 0x01846030

#define L2EDCMD 0x01846008

#define SMEDCC 0x0BC00010

/* Enable L1P EDC */

*(volatile unsigned int *)(L1PEDCMD) = 0x1; //Set EN(bit0)=1

/* Enable EDC L2EDCEN, set DL2CEN(bit0),PL2CEN(bit1),DL2SEN(bit2),PL2SEN(bit3),SDMAEN(bit4)=1 */

*(volatile unsigned int *)(L2EDCEN) |= 0x1F;

/* Enalble L2 EDC */

*(volatile unsigned int *)(L2EDCMD) = 0x1;

/* Enalbe MSMC EDC */

*(volatile unsigned int *)(SMEDCC) &= 0x7FFFFFFF; //Clear SEN(bit31)=0

*(volatile unsigned int *)(SMEDCC) |= 0x40000000; //Set ECM(bit30)=1

/* undocumented register in data manual

* Bit 0 of this register is supposed to give the status of PCIe PLL lock*/

#define PCIE_STS_REG 0x262015C

/* Workaround for PCIe boot mode support for C6678/C6670 */

/* This is a temporary workaround should be removed once fixed in RBL */

/* PCIe Config register base on C6678/C6670 */

#define PCIE_BASE_ADDR 0x21800000

/* PCIe Application registers */

#define PCIE_APP_CMD_STATUS 0x4

#define PCIE_APP_OB_SIZE 0x30

#define PCIE_APP_MSI0_IRQ_ENABLE_SET 0x0108

#define PCIE_APP_LEGACY_A_IRQ_ENABLE_SET 0x0188

#define PCIE_APP_LEGACY_B_IRQ_ENABLE_SET 0x0198

#define PCIE_APP_LEGACY_C_IRQ_ENABLE_SET 0x01a8

#define PCIE_APP_LEGACY_D_IRQ_ENABLE_SET 0x01b8

#define OB_OFFSET_INDEX0 0x200

#define OB_OFFSET_HI0 0x204

#define OB_OFFSET_INDEX1 0x208

#define OB_OFFSET_HI1 0x20C

#define PCIE_APP_IB_BAR0 0x300

#define PCIE_APP_IB_START0_LO 0x304

#define PCIE_APP_IB_START0_HI 0x308

#define PCIE_APP_IB_OFFSET0 0x30C

#define PCIE_APP_IB_BAR1 0x310

#define PCIE_APP_IB_START1_LO 0x314

#define PCIE_APP_IB_START1_HI 0x318

#define PCIE_APP_IB_OFFSET1 0x31C

#define PCIE_APP_IB_BAR2 0x320

#define PCIE_APP_IB_START2_LO 0x324

#define PCIE_APP_IB_START2_HI 0x328

#define PCIE_APP_IB_OFFSET2 0x32C

#define PCIE_APP_IB_BAR3 0x330

#define PCIE_APP_IB_START3_LO 0x334

#define PCIE_APP_IB_START3_HI 0x338

#define PCIE_APP_IB_OFFSET3 0x33C

#define PCIE_APP_SERDES_CFG0 0x390

#define PCIE_APP_SERDES_CFG1 0x394

/* PCIe Local Configuration registers */

#define PCIE_VENDER_DEVICE_ID 0x1000

#define PCIE_STATUS_CMD 0x1004

#define PCIE_CLASSCODE_REVID 0x1008

#define PCIE_BAR0 0x1010

#define PCIE_BAR1 0x1014

#define PCIE_BAR2 0x1018

#define PCIE_BAR3 0x101c

#define PCIE_BAR4 0x1020

#define PCIE_BAR5 0x1024

#define PCIE_DEVICE_CAP 0x1074

#define PCIE_DEV_STAT_CTRL 0x1078

#define PCIE_LINK_STAT_CTRL 0x1080

#define PCIE_ACCR 0x1118

#define PCIE_PL_LINK_CTRL 0x1710

#define PCIE_DEBUG0 0x1728

#define PCIE_PL_GEN2 0x180C

/* SERDES Configuration registers */

#define PCIE_SERDES_CFG_PLL 0x2620358

/* Power up PCIe */

devicePowerPeriph (TARGET_PWR_PCIE);

for(i=0; i<1000; i++) asm (" NOP");

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_APP_SERDES_CFG0), 0x00062320); /* ss clock */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_APP_SERDES_CFG1), 0x00022320); /* ss clock */

/* Wait for PCIe PLL lock */

while(!(DEVICE_REG32_R(PCIE_STS_REG) & 1));

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_CLASSCODE_REVID), 0x04800001); /* class 0x04, sub-class 0x80, Prog I/F 0x00, Other multimedia device */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_LINK_STAT_CTRL), 0x10110080); /* extended sync, slot_clk_cfg = 1 */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_VENDER_DEVICE_ID), 0xb005104c); /* Vendor and Device ID */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_DEVICE_CAP), 0x288701); /* L0 = 4, L1 = 3 */

reg = DEVICE_REG32_R(PCIE_BASE_ADDR + PCIE_LINK_STAT_CTRL) & 0x0000FFFF;

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_LINK_STAT_CTRL), reg | 0x00010000);

reg = DEVICE_REG32_R(PCIE_BASE_ADDR + PCIE_PL_LINK_CTRL) & 0x0000FFFF;

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_PL_LINK_CTRL), reg | 0x00010000);

//DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_APP_OB_SIZE ), 0x00000003); /* OB_SIZE = 8M */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_PL_GEN2 ), 0x0000020F); /* num_fts = 0xF*/

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_APP_CMD_STATUS), 0x0020); /* Set dbi_cs2 to allow access to the BAR registers */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_BAR0), 0x00000FFF); /* 4K */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_BAR1), 0x00FFFFFF); /* 4K */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_BAR2), 0x00000000); /* 4K */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_BAR3), 0x00000000); /* 4K */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_BAR4), 0x00000000); /* 4K */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_BAR5), 0x00000000); /* 4K */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_APP_CMD_STATUS), 0x0); /* dbi_cs2=0 */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_STATUS_CMD ), 0x00100146); /* ENABLE mem access */

//DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_DEV_STAT_CTRL), 0x0000281F); /* Error control */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_DEV_STAT_CTRL), 0x0000000F); /* Error control */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_ACCR ), 0x000001E0); /* Error control */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_APP_IB_BAR0 ), 0x00000001);

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_APP_IB_START0_LO), 0x70000000);

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_APP_IB_START0_HI), 0x00000000);

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_APP_IB_OFFSET0 ), 0x11800000);

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_APP_CMD_STATUS), 0x0000004);

//DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_BAR0), 0x00000000); /* non-prefetch, 32-bit, mem bar */

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_BAR1), 0x70000000);

DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_APP_CMD_STATUS), 0x0000001);

//DEVICE_REG32_W ((PCIE_BASE_ADDR + PCIE_APP_CMD_STATUS), 0x0000007); /* enable LTSSM, IN, OB */

while((DEVICE_REG32_R(PCIE_BASE_ADDR + PCIE_DEBUG0) & 0x11)!=0x11); /* Wait for training to complete */

/* Wait for the Boot from Host */

for(;;)

{

}

}