Hi,

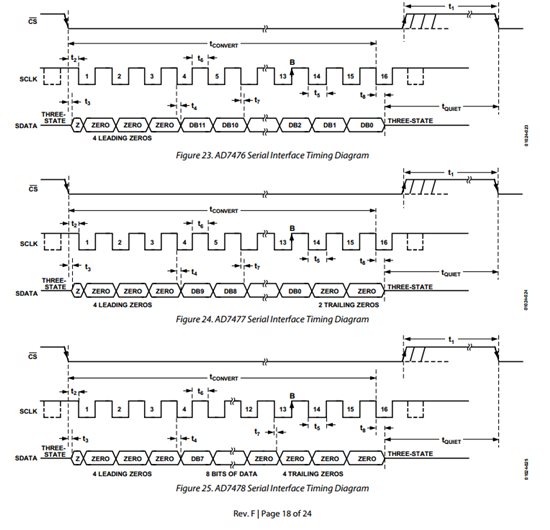

I am upgrading from a tms320vc5409 to tms320c6745 and would like to interface the McASP to the AD7476. The McBSP on the 5409 was able to generate the proper chip select which is low for 16 bits and then high for 4 bits. I cannot find a way to configure the McASP to do the same. Can anyone provide a suggestion?

This is the ADC I am using:

http://www.analog.com/static/imported-files/data_sheets/AD7476_7477_7478.pdf

The requirements as I see it are as follows.

1) Run the clock at 20MHz to get a 1MHz sampling rate.

2) /CS (framesync) needs to be low for 16-clocks to read the input sample and then high for 4 clocks to re-initiate tracking.

I have placed the McASP in Burst Mode, as I see this is the only alternative to I2S mode, but I can only seem to get a single pulse framesync.

I would appreciate any suggestions.

Thanks,

Rich