Hi

For our development testing using the custom board, we would like to measure PLL_DSP. For this, we intend to utilise the CLKOUT0 pin.

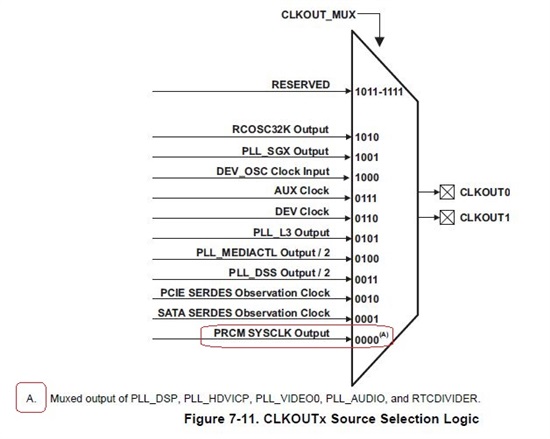

From the TRM, we understand that we need to tweak the CLKOUT_MUX register and set bits 3-0 as 0x0 [Source is PRCM_SYSCLK_OUT]. We identified PRCM_SYSCLK_OUT based on the CLKOUTx Source Selection Logic diagram from the datasheet as shown below.

But from the attached image, it seems like PRCM_SYSCLK_OUT is a muxed output of PLL_DSP, PLL_HDVICP, PLL_VIDEO0, PLL_AUDIO, and RTCDIVIDER.

How do we choose to output PLL_DSP only from above muxed options? Please correct us if i am missing something.

Padmanabhan