Hello,

One of my important customer made their custom C6655 board.

And, they are evaluating EMIF16 NOR boot on it.

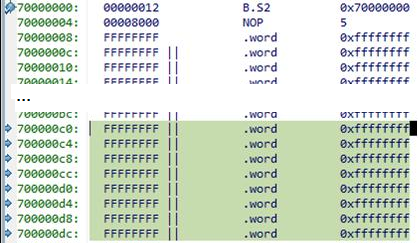

They are putting loop forever operation code (0x00000012) on EMIF base address (0x70000000).

And, they can see PC jumps to the address (0x70000000) after reset.

But, actual operation is unexpected. It just pass through the loop forever.

When I put the same operation code (0x00000012) in internal RAM area, expected operation can be observed.(Loop forever)

Question)

- Have you ever encountered the issue like this?

- Is there any restriction at 0x70000000?

Any advise would be appreciate.

Best regards, RY