Hi all

I am using TI platform for AM335x, with Am335x EVM Board, download SDK from the following URL

http://software-dl.ti.com/sitara_linux/esd/AM335xSDK/06_00_00_00/index_FDS.html

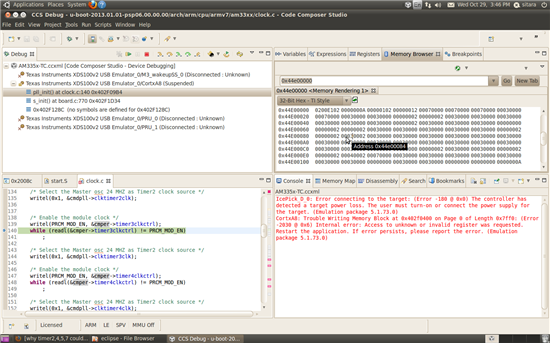

I'm trying to enable the timer2~7 using the following code, and the result shows the timer3 and timer6 couldn't enable succeed (cmper->timer3clkctrl & cmper->timer6clkctrl) but timer2,4,5,7 could . I feel confused, does anyone know what's wrong with my code :-(

/*

* Force power domain wake up transition

* Ensure that the corresponding interface clock is active before

* using the peripheral

*/

static void power_domain_wkup_transition(void)

{

writel(PRCM_FORCE_WAKEUP, &cmper->l3clkstctrl);

writel(PRCM_FORCE_WAKEUP, &cmper->l4lsclkstctrl);

writel(PRCM_FORCE_WAKEUP, &cmwkup->wkclkstctrl);

writel(PRCM_FORCE_WAKEUP, &cmper->l4fwclkstctrl);

writel(PRCM_FORCE_WAKEUP, &cmper->l3sclkstctrl);

//Enable the domain power state for Timer2~7

writel(0x1 << 13, &cmper->l4lsclkstctrl);/*Timer 7*/

writel(0x1 << 28, &cmper->l4lsclkstctrl);/*Timer 6*/

writel(0x1 << 27, &cmper->l4lsclkstctrl);/*Timer 5*/

writel(0x1 << 16, &cmper->l4lsclkstctrl);/*Timer 4*/

writel(0x1 << 15, &cmper->l4lsclkstctrl);/*Timer 3*/

}

/*

* Enable the peripheral clock for required peripherals

*/

static void enable_per_clocks(void)

{

/* Enable the control module though RBL would have done it*/

writel(PRCM_MOD_EN, &cmwkup->wkctrlclkctrl);

while (readl(&cmwkup->wkctrlclkctrl) != PRCM_MOD_EN)

;

/* Enable the module clock */

writel(PRCM_MOD_EN, &cmper->timer7clkctrl);

while (readl(&cmper->timer7clkctrl) != PRCM_MOD_EN)

;

/* Select the Master osc 24 MHZ as Timer7 clock source */

writel(0x1, &cmdpll->clktimer7clk);

/* Enable the module clock */

writel(PRCM_MOD_EN, &cmper->timer2clkctrl);

while (readl(&cmper->timer2clkctrl) != PRCM_MOD_EN)

;

/* Select the Master osc 24 MHZ as Timer2 clock source */

writel(0x1, &cmdpll->clktimer2clk);

/* Enable the module clock */

writel(PRCM_MOD_EN, &cmper->timer3clkctrl);

while (readl(&cmper->timer3clkctrl) != PRCM_MOD_EN)

;

/* Select the Master osc 24 MHZ as Timer3 clock source */

writel(0x1, &cmdpll->clktimer3clk);

/* Enable the module clock */

writel(PRCM_MOD_EN, &cmper->timer4clkctrl);

while (readl(&cmper->timer4clkctrl) != PRCM_MOD_EN)

;

/* Select the Master osc 24 MHZ as Timer4 clock source */

writel(0x1, &cmdpll->clktimer4clk);

/* Enable the module clock */

writel(PRCM_MOD_EN, &cmper->timer5clkctrl);

while (readl(&cmper->timer5clkctrl) != PRCM_MOD_EN)

;

/* Select the Master osc 24 MHZ as Timer5 clock source */

writel(0x1, &cmdpll->clktimer5clk);

/* Enable the module clock */

writel(PRCM_MOD_EN, &cmper->timer6clkctrl);

while (readl(&cmper->timer6clkctrl) != PRCM_MOD_EN)

;

/* Select the Master osc 24 MHZ as Timer6 clock source */

writel(0x1, &cmdpll->clktimer6clk);

....

....

....

}

/*

* Configure the PLL/PRCM for necessary peripherals

*/

void pll_init()

{

/* Start at 550MHz, will be tweaked up if possible. */

mpu_pll_config(MPUPLL_M_300);

core_pll_config(OPP_50);

per_pll_config();

/* Enable the required interconnect clocks */

enable_interface_clocks();

/* Power domain wake up transition */

power_domain_wkup_transition();

/* Enable the required peripherals */

enable_per_clocks();

}