Dear All,

I am working with DVRRDK_04.00.00.03 on a customized board, as to obtain a precise video frequency of the video we use AUXOSC (27MHz external crystal) as the reference clock.

The following is our modified code:

/var/works/DVRRDK_04.00.00.03/ti_tools/linux_lsp/kernel/linux-dvr-rdk/drivers/video/ti81xx/vpss/system.c:

#define TI814X_OSC_FREQ (27 * MHZ) //20

DVRRDK_04.00.00.03/ti_tools/hdvpss/dvr_rdk_hdvpss/packages/ti/psp/platforms/ti8107/src/vps_platformTI8107.c

#define VPS_TI8107_EVM_OSC_FREQ (27u * VPS_TI8107_MHz) //20u

DVRRDK_04.00.00.03/ti_tools/linux_lsp/kernel/linux-dvr-rdk/arch/arm/mach-omap2/clock814x_data.c:

/* Additional clock source */

static struct clk osc1_clkin_ck = {

.name = "osc1_clkin_ck",

.ops = &clkops_null,

.rate = 27000000, //22579000, /* Typically at 27M or 22.579MHz */

.flags = RATE_IN_TI814X | RATE_IN_DM385 | RATE_IN_TI811X,

};

DVRRDK_04.00.00.03/ti_tools/linux_lsp/kernel/linux-dvr-rdk/arch/arm/mach-omap2/board-ti8148evm.c:

static void __init ti8148_evm_init(void)

{

...

//change clk parent

struct clk *parent, *child;

parent = clk_get(NULL, "osc1_clkin_ck");

child = clk_get(NULL, "video1_dpll_clkin_ck");

clk_set_parent(child, parent);

clk_put(child);

clk_put(parent);

}

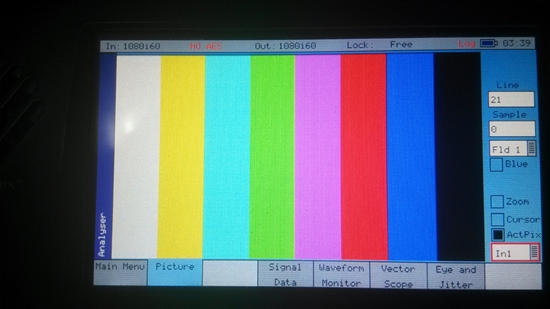

It probably can work, but the video output is abnormal, It looks like that the Vsync is not synchronized.

Please refer to the the attached video!

But when I enable the HD_VENC self test mode, I can get a good video output.

root@dm810x:/opt/dvr_rdk/ti810x# ./bin/mem_rdwr.out --rd 4810a000

0x4810a000: 5421305A

root@dm810x:/opt/dvr_rdk/ti810x# ./bin/mem_rdwr.out --wr 4810a000 5421b05a

ORG 0x4810a000: 5421305a

NEW 0x4810a000: 5421b05a

root@dm810x:/opt/dvr_rdk/ti810x#

Can anybody give me any suggestion on this issue?

Thanks!

Sivan Tse