hello all,

We are planning to use the am3359 platform for some adc applications and the speed of the adc module is our main consideration.

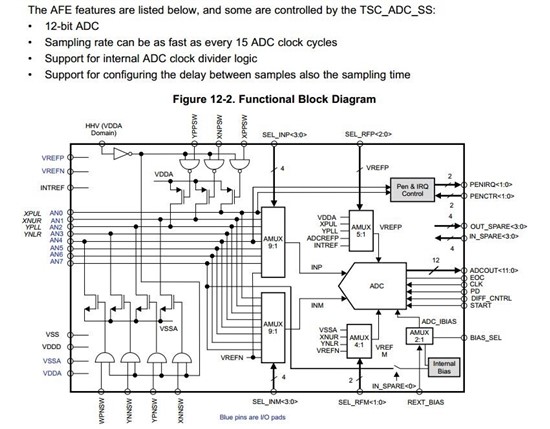

We have checked some official materials, and it seems the sampling frequency of the adc module in am3359 is only 200K (see the following figure grabbed from one datasheet of am3359):