Hi

I want to operate the VPBE in slave mode with external clocking. The clocks and synchronization come from a FPGA.

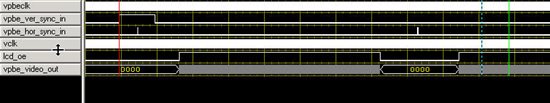

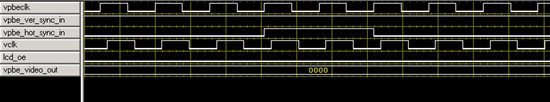

After changing the registers of VPBE what I see on the logic is VSYNC and HSYNC are correct; output clock is ok; LCD_OE ok. The only problem is with the data that is not correct. I send to output a fix pattern but receive different data, also which change from frame to frame.

The most strange is that after I close the application, the data is changing from frame to frame.

Anyone has some idea? There is somebody using VPBE digital output in slave mode?

I will appreciate your help.

Best regards

Marcel