My DM8148 board has two MT41J128M16-125 DDR3 chips, use DDR Controller 0 interface.

/*Program the DMM to Access EMIF0 and EMIF1*/

WR_MEM_32(DMM_LISA_MAP__0, 0x0);

WR_MEM_32(DMM_LISA_MAP__1, 0x0);

WR_MEM_32(DMM_LISA_MAP__2, 0x0);

WR_MEM_32(DMM_LISA_MAP__3, 0x80500100);

Timings configuration :

//DDR3 400 MHz - CL=6,CWL=5

#define DDR3_EMIF_TIM1_DEFINE_400 0x0AAAD4DB

#define DDR3_EMIF_TIM2_DEFINE_400 0x20437FDA

#define DDR3_EMIF_TIM3_DEFINE_400 0x507F83FF

#define DDR3_EMIF_REF_CTRL_DEFINE2_400 0x00000C30

#define DDR3_EMIF_SDRAM_CONFIG_DEFINE_400 0x638412B2

#define DDR3_EMIF_DDRPHYCR_DEFINE_400 0x00170209

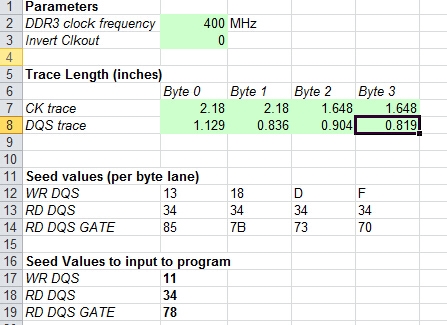

The RatioSeed_TI814x.xls configuration as follows:

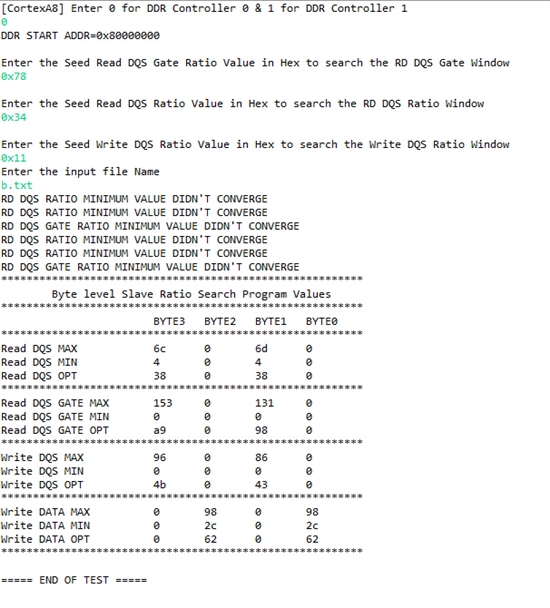

The results obtained after running DDR3_SlaveRatio_ByteWiseSearch_TI814x.out:

BYTE2 and BYTE0 are always zero, can not converge

2275.400MHz_DM814x_DDR_Controller_Register_Configuration_spreadsheet_v1.0.xlsx