Hi,

I have a question about SYSCLK of 66AK2H12.

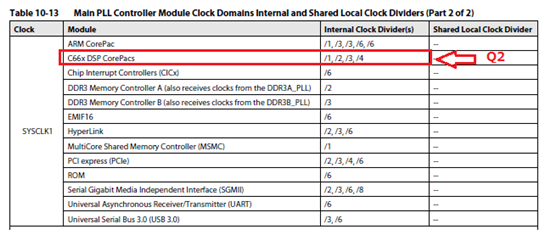

Q1. What is the SYSCLK1 frequency at above power sequence?

If input Clock source (SYSCLK N/P) is 100Mhz, is SYSCLK1 100Mhz?

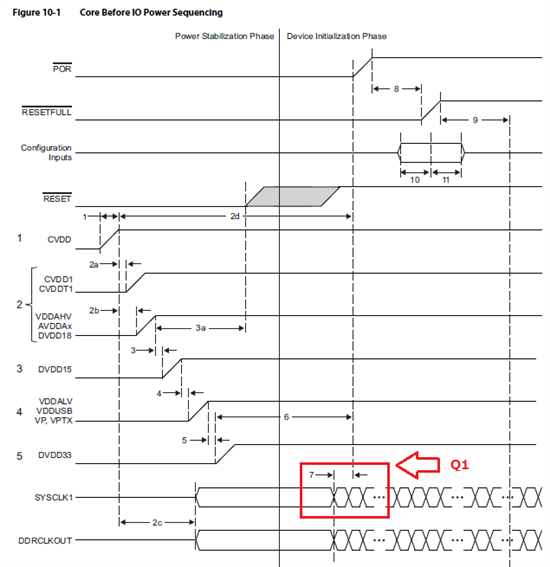

Q2. Is it means that c66x DSP Core Pacs frequency is SYSCLK1/1?

Please tell me what means "/2, /3, /4" has been described in the above table.

Q3. I think that Internal Clock Diveiders and Shared Local Clock Divider that described in Table 10-13 can

not be changed by user.

For example, Boot Config Module is always running at SYSCLK1/6.

My thinking is correct?

Best regards,

H.U