Other Parts Discussed in Thread: AM3874, AM3892, AM3871, AM3894, AM3352

Hi,

We have a new custom board based on AM3874. We had used this CPU before on a different project. Both boards are using U-Boot version based on EZSDK 5.05.02.0.

Here’s the quick info on this new board:

- CPU is configured for 720MHz and DDR3 runs at 400MHz

- Will boot from NOR flash

- Using 1 x Micron MT41K256M16HA-125 DDR3 chip (16-bit data interface, 512MB size) connected to EMIF0

- EMIF0 is configured for 16-bit data bus width (D0 – D15).

- EMIF1 is not used

- AM3874 DDR3 Registers are configured as:

#define DDR3_EMIF_READ_LATENCY 0x00170209

#define DDR3_EMIF_TIM1 0x0AAAD4DB

#define DDR3_EMIF_TIM2 0x266B7FDA

#define DDR3_EMIF_TIM3 0x501F867F

#define DDR3_EMIF_REF_CTRL 0x00000C30

#define DDR3_EMIF_SDRAM_CONFIG 0x61C05332

#define DDR3_EMIF_SDRAM_ZQCR 0x50074BE4

- LISA map is configured as:

#define PG2_1_DMM_LISA_MAP__0 0x0

#define PG2_1_DMM_LISA_MAP__1 0x0

#define PG2_1_DMM_LISA_MAP__2 0x0

#define PG2_1_DMM_LISA_MAP__3 0x80500100

DDR3 has been quickly tested using Code Composer. DDR3 access seems ok when reading/writing in Code Composer Memory Window. Was able to successfully program u-boot in NOR flash through Code Composer. However, board is not booting up properly. The CPU is stuck on the data abort exception default handler (0x2008c).

The first board we developed based on the AM3874 also boots from NOR flash. But, it uses 32-bit DDR3 (4 8-bit DDR3 Micron chips) compared to the 16-bit DDR3 in this new design.

AFAIK, the only change that must be done in u-boot is the NARROW_MODE bits (14:15) in SDRAM Configuration Register = 0x61C05332.

- Is there any other changes in u-boot that is required to support 16-bit data bus width DDR3 in AM3874?

- Did anybody succeeded in using just 16-bit data bus width DDR3 instead of the usual 32-bit?

- Is it required to use thumb instructions instead of the ARM 32-bit instructions if we are only using 16-bit data bus width?

I was able to put a breakpoint in start_armboot() in u-boot and it fails when doing the first memset(). The issue appears to be incorrect instructions when determining the address of (gd_t *) gd and the sizeof(gd_t). Looking closely, the relocated code from NOR flash to DDR3 is incorrect in the lower 8-bytes of every 16-byte address (e.g. 0x807000A0, 0x807000B0, etc.). I then realized that the byte-wise SW leveling values I am currently using is for the DM8148 EVM board.

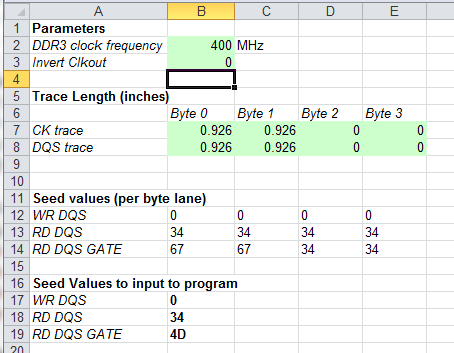

So, I tried to get the correct ratio values for the DDR3 PHY configuration. And then another issue occurs. Unlike our previous board where the CK and DQS trace lengths are about 3.5 to 4 inches long, this new board only uses 0.926 inches on both CK and DQS. Byte-wise SW leveling gave a result of 0 on all the parameters. Word-wise SW leveling gives a bunch of errors regarding RD DQS/RD DQS GATE/WR DATA RATIO MINIMUM VALUE DIDN’T CONVERGE and then gave a result of 0 on all the parameters.

Thus, a new set of questions came up.

- What values should be entered for Byte 2 and 3 if only 16-bit data bus width is used? We entered zero in our case.

- Does both DDR3 byte-wise and word-wise software leveling requires that 4-byte lane is used? Does the DDR3_SlaveRatio_ByteWiseSearch_TI814x.out and DDR_slave_ratio_search_TI814x.out know when only 2-byte lanes are used instead of 4-byte lanes?

- If the CK and DQS trace have equal length, what should the value of Invert Clkout be? Is it 0 or 1?

- What does it mean when Software Leveling is giving a result of 0 on all the required parameters? What does the error RD DQS/RD DQS GATE/WR DATA RATIO MINIMUM VALUE DIDN’T CONVERGE means?

- Is there a minimum DDR3 CK and DQS trace length for AM3874?

Anyway, since 0 does not seem to be an appropriate value for the DDR3 PHY configuration, I ended up using the values we were using for our previous board (even though the trace is 4 inches compared to less than 1 inch). A funny thing happened after making this change. The error in start_armboot() where gd address is incorrect was suddenly fixed. Thus, u-boot goes further. However, it will still do a data abort at a later place. U-Boot serial console message is still not present. Thus, it looks like the issue is a DDR3 configuration issue.

Any help is greatly appreciated.

Regards,

Maynard