Hi,

My customer used SRIO in the following condition.

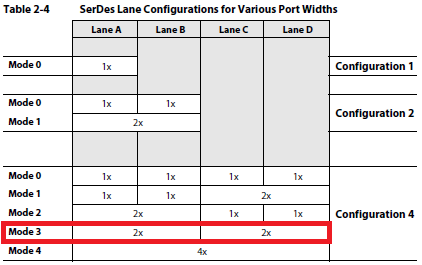

Table 2-4 SerDes Lane Configurations for Various Port Widths(SPRUGW1B)

Configuration 4 Mode3 : x2 lane, x2 port

Q1. Do the SWRITE, NWRITE and NWRITE_R packets handled correctly when port A and port B receive packets at the same time which containing same SRCID?

I am minding if port A or B returns the wrong response to the other, when both ports are recieved packet containing same SRCID.

Q2. If multiple ports receive packets containing the same SRCID, dose the following constrain in SRIO UG consider

the receiving ports? That means that SRIO peripheral handles these packets as "same SRCID transaction" or NOT.

Q3. When each ports receive the different priority packet at same time:

Q3-1. Does high-priority packet be processed at first? If so, could you explain the scheduling scheme among multiple ports?

Q3-2. During processing the lower priority packet, when does the SRIO peripheral switch to the higher packet?

Best regards,

H.U