Hi,

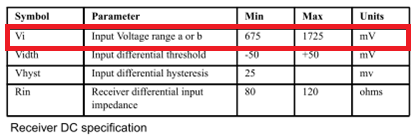

I think that serdes interface as SRIO require the AC-coupling capacitor and external termination.

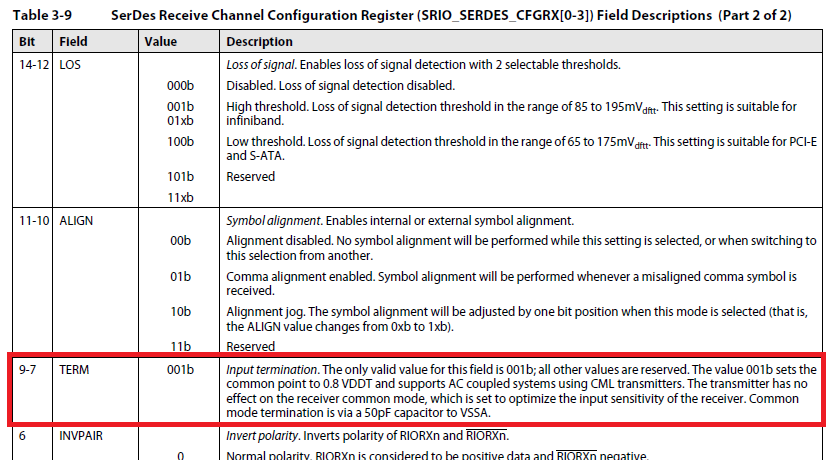

However, SRIO UG(SPRUGW1B) of 66AK2H12 described as follows:

So, does this device not need external terminations because it is contain internal termination resistors?

Best regards,

H.U