Dear Sir,

We are using AM335x microprocessor in one of our project. We are using TI-SDK linux package i.e. ti-sdk-am335x-evm-06.00.00.00 for linux kernel source.

1) Case 1:

We have written a simple kernel driver for having GPIO input pin as interrupt and configured a irq_handler routine for this GPIO pin on signal rising edge. This pulse comes on GPIO input at every 1 second and this pulse is very precise and accurate as it is coming from GPS receiver module.

I am able to get the interrupt routine called on every pulse on this configured GPIO pin as interuupt source. But, the signal latency is too much. I am checking the latency by making another GPIO pin as output "LOW" on every interrupt routine Called. I am checking the latency on CRO by keeping my input pulse on trigger and measuring the duration between input pulse and generated GPIO output pulse.

I found that interrupt latency is around 16 t0 20 microsecods. It seems very high as AM335x processor is running at 720 MHz cpu clock frequency. Again, this latency is not stable though my GPIO input pulse is stable. The interrupt latency varies from 16 us to 25 us randomly. There is only kernel driver running and no user application code running.

Query:

1) Why the interrupt latency is very high as it should be in nanoseconds only if processor is running at 720 MHz ?

2) Why the interrupt latency is not stable at said value, as it varies from 16us to 25us?

2) Case 2:

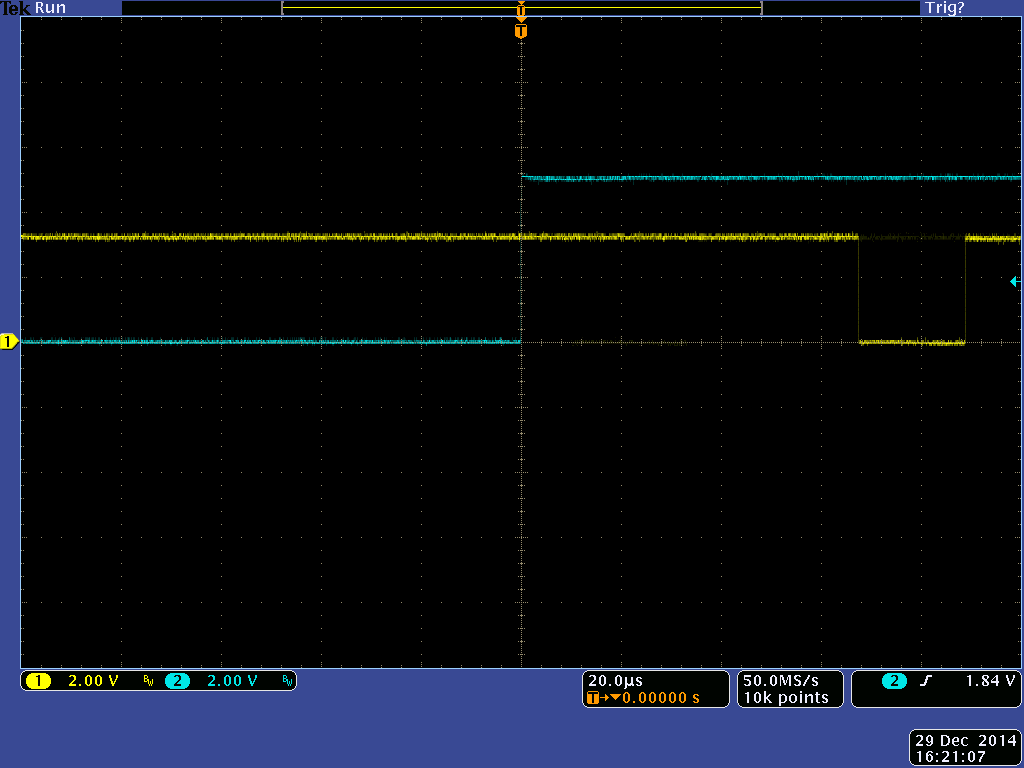

In similar above case, if i run a simple user application code, there is jump of latency from 20us directly to 65us approx. randomly (please check below image). Also the pulse width of pulse

output have increased significantly as compare to case 1.

As my user application code is very simple blank code, having only while(1) loop in void main(). Please find the attached code.

Why my GPIO output jumps from 20us to 65 us (i.e. interrupt latency) randomly though there is no system calls from user applicaiton code as this jump in case 1.

Query:

1) Why the interrupt latency jumps for such a large value if user application code is running?

All the above readings are taken on calibrated 1 GHz CRO and directly on GPIO bank port pin of AM335x processor.

I will appreciate for any kind of support provided.

Regards,

Ajay