Other Parts Discussed in Thread: DA8XX

Dear All,

in our design, We have used LCDC to control a 24 bpp TFT display(LMS700kF07). We are facing LCD flickering issue in 1 device out of 20 devices after a long run(1 to 2 Hours). When this issue occurs it is showing following error.

<3>[ 741.282379] LCDC sync lost or underflow error occured

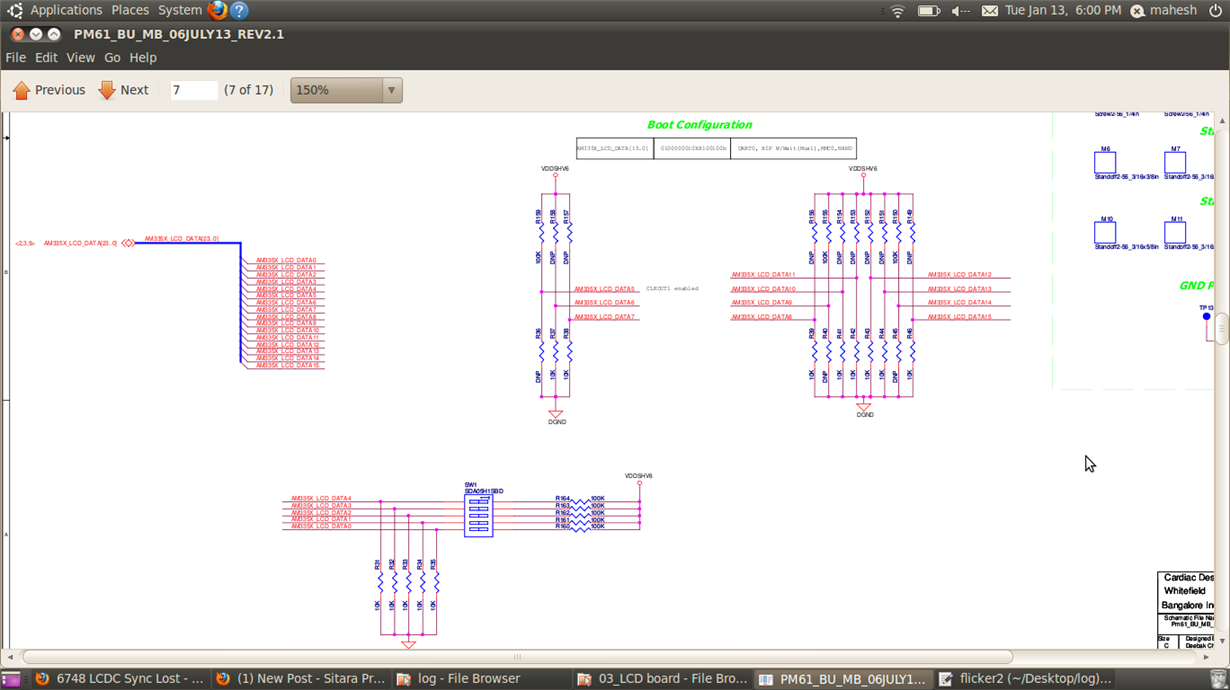

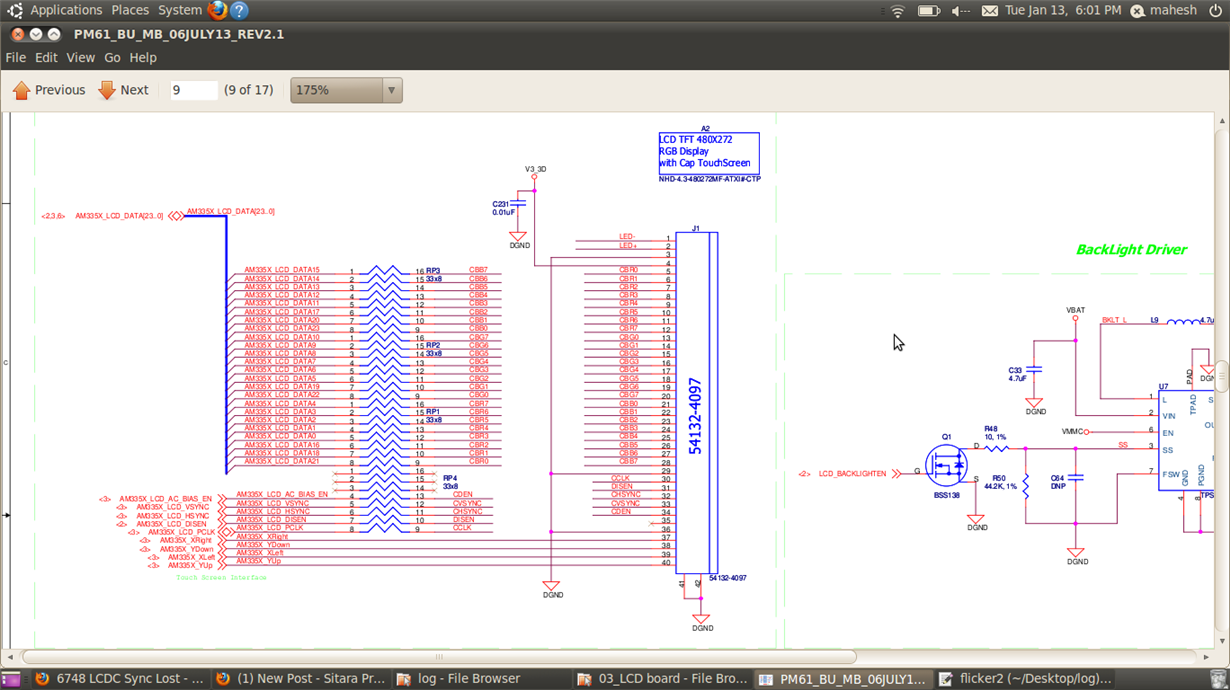

I am not able to get why we are facing this issue in 1 device. Is it a hardware issue?. The schematics of Boot configuration & LCD interface is as follows.

Fig: Boot Configuration

Fig : LCD Interface

Please reply me as soon as possible. Please suggest me what could be the issue is?

Thanks and Regards,

Bhairu