Hi all

In the LP1 design of our custom board, we had used both DDR0 and DDR1 Memory controller - working very well. We used 2GB in total(comprising a total of 4 chips - each of 512MB) - 1GB for each memory controller. However, we found that the total memory available was overkill for our application and decided to reduce the capacity from 2GB to 1GB to save cost.

For the LP2 build of our custom board, we are planning to use only DDR0 Memory Controller of the DM8148. We would like to keep the PCB layout the same since changes the DDR interface layout is time consuming and likely to hit our schedules. Also, we do not prefer to make changes to a working solution.

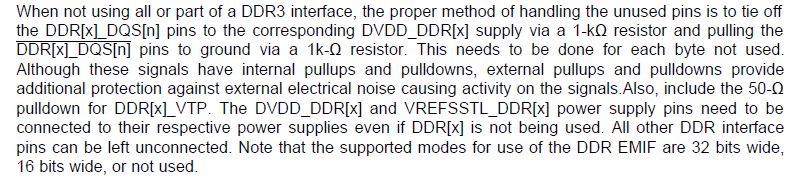

Hence, we are thinking of using back the same layout for DDR subsytem from the LP1 phase and just leave the memory chips relevant to DDR1 interface unmounted. From the point of view of hardware, we came across this from the DM8148 datasheet.

The question is: Are we likely to face any issue on the DDR0 interface since the datasheet clearly mentions there are internal pullup/pulldown on DQSp/DQSn respectively? It also mentions using external pullup/pulldown resistors! Clearly, if it is just an option, we do not prefer to make changes on the layout. Any suggestions?

Apart from this, is there any register setting we need to take care of to power down the DDR1 interface so as to avoid being affected by noise?

Also, with respect to the internet pullup/pull down for the differential strobe lines- are these, again, register controlled?

Regards,

KS Padmanabhan