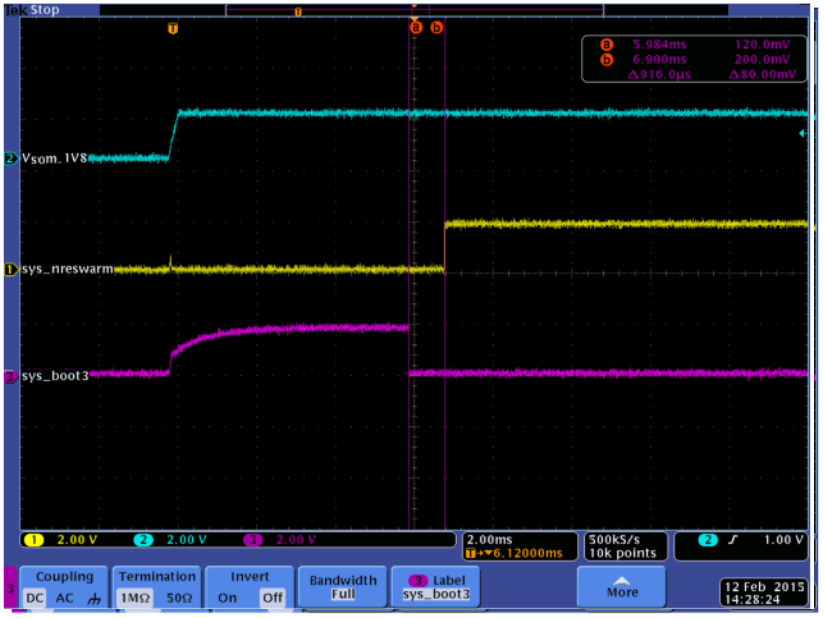

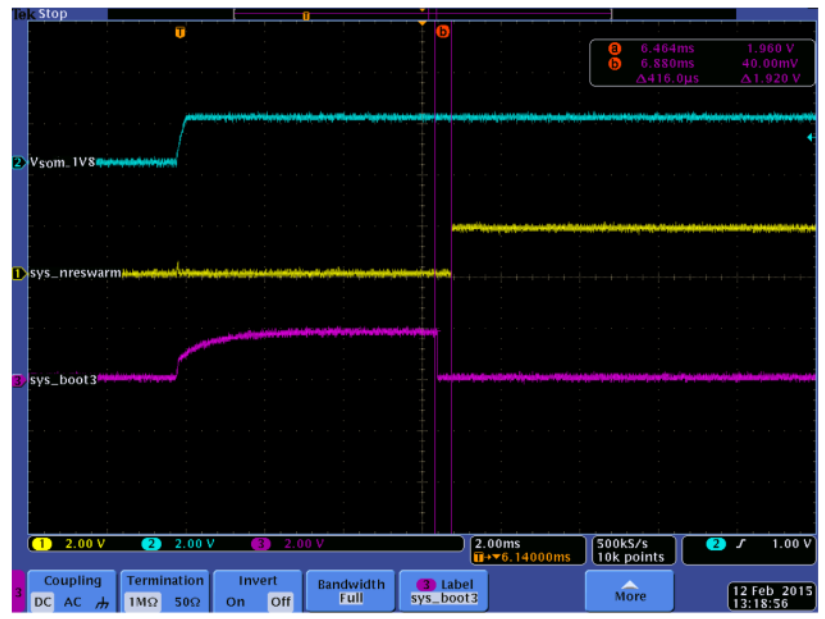

On the DM3730 processor the sys_boot signals are shared with LCD data signals. Since the LCD is not yet powered until after the sys_boot signals are latched this is putting a load on the sys_boot signals at reset. This load through the ESD diodes is causing the sys_boot signals to be incorrectly latched. We can alter the load by changing the bulk capacitance on the LCD I/O voltage rail. However, we don't know when the sys_boot signals are being latched with respect to the SYS_nRESWARM signal. My questions are the following.

When are the SYS_BOOT signals being latched by the processor? I did find information in the documentation is that they are latched “following a power-on reset”. Are they latched on the rising edge of SYS_nRESWARM? Or afterwards? If afterwards, what is the minimum and maximum time they are latched?