Other Parts Discussed in Thread: TMS320C6678, SYSBIOS

Hi All,

I have the following representation for establishment of API for DSP

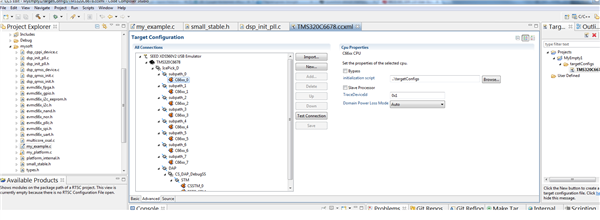

1. I create the project in CCSv5 and to upload it to DSP use my emulator SEED-XDS560v2

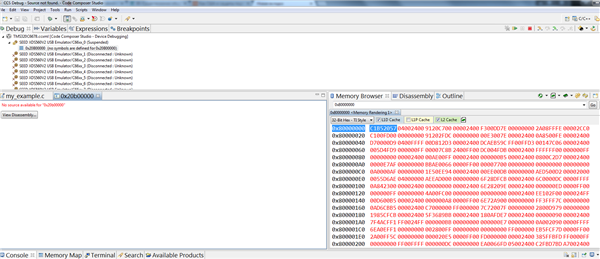

2.This API is not by work API to DSP because it requires initialization DDR3 memory and PLL using GEL file

3.GEL file is not part my API and loaded to DSP only by emulator after connect with any core

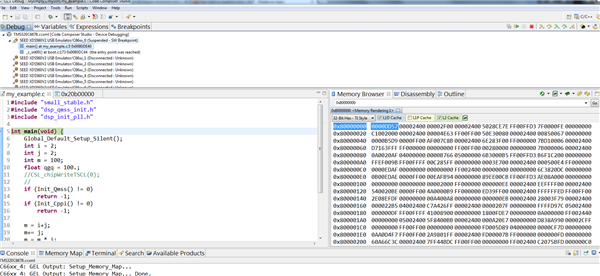

4.I can not create API if I use memory map to RTSC with "Program.sectMap[.text] = "DDR3" " don't use GEL file

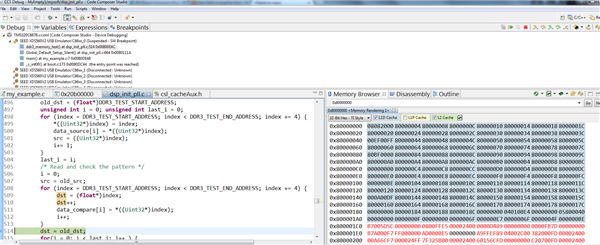

I can create API for DSP and create memory map using RTSC if I use only Shared Memory - "Program.setMap[.text] = "MSMCSRAM" " and I can init DDR3 inside my API. (I create this example for QMSS)

I have questions - what restriction am I have in this case - how I can create memory map type as "Program.sectMap[.text] = "DDR3" " if I not used GEL file

Or I misunderstood. the process of creating chipboard applications?

PS. I believe that I should have a binary boot file that I write into flush memory for automatically download

Best regards,

Oleg