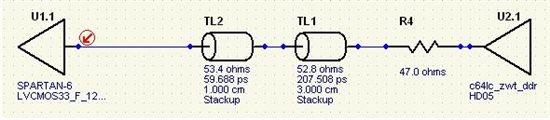

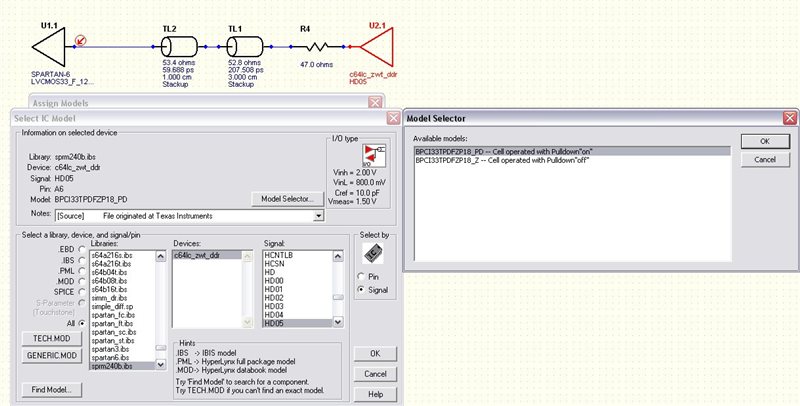

I get some strange results when I simulate the DSP (TMS320C6424) as TX and the FPGA (xilinx spartan 6) as RX. I have downloaded the latest Ibis models so this should be allright. A 47 Ohm series termination is used to reduce overshoot.

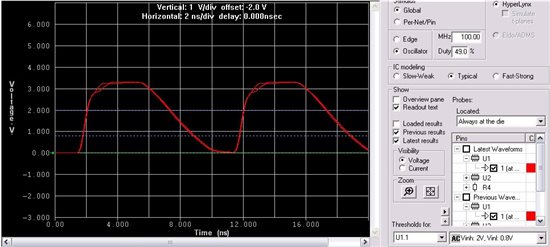

As seen below there is something unharmonic, because Risetime is 0.62ns and fall time is 2.5ns @100mHz causing my low period to be rather short.

Can someone please explain me what is going on?

Thanks in advance