We have four c6678 DSPs(with SRIO port 0 of each dsp only) connected to a switch(cps1616) on a custom board. Our aim is to establish communication between any two dsp, say DSP0 and DSP1 through the switch. Our desired configuration is 1x and 2.5Gbps speed. We tried running loopbackDioIsr project on DSPs first in loopback mode and they were successful . We made the necessary changes to run loopbackDioIsr project in normal mode by changing mode from loopback to normal and swapped the source and destination ID in second dsp, DSP1. We made routing table in switch through switch registers. We followed this thread:  We also made sure that before any transfer occur, respective ports in switch are in OK state. The problem is that, in srio switch as soon as transfer from DSPs starts, the port shows output error and input error. We tried to run the code snippet(maintenanceReadReg) given in above thread by Brandy but it returned error that "ISR didn't happen within set time". We contacted IDT too for this error and they are suggesting us to do routing through maintenance packets but I have little idea about how to do it.

We also made sure that before any transfer occur, respective ports in switch are in OK state. The problem is that, in srio switch as soon as transfer from DSPs starts, the port shows output error and input error. We tried to run the code snippet(maintenanceReadReg) given in above thread by Brandy but it returned error that "ISR didn't happen within set time". We contacted IDT too for this error and they are suggesting us to do routing through maintenance packets but I have little idea about how to do it.

I have the following questions:

1. Is there any register which stores number of packets sent through DSP? So that we

can confirm that some packets have been sent out of DSP.

2. How can we configure switch through maintenance packets?

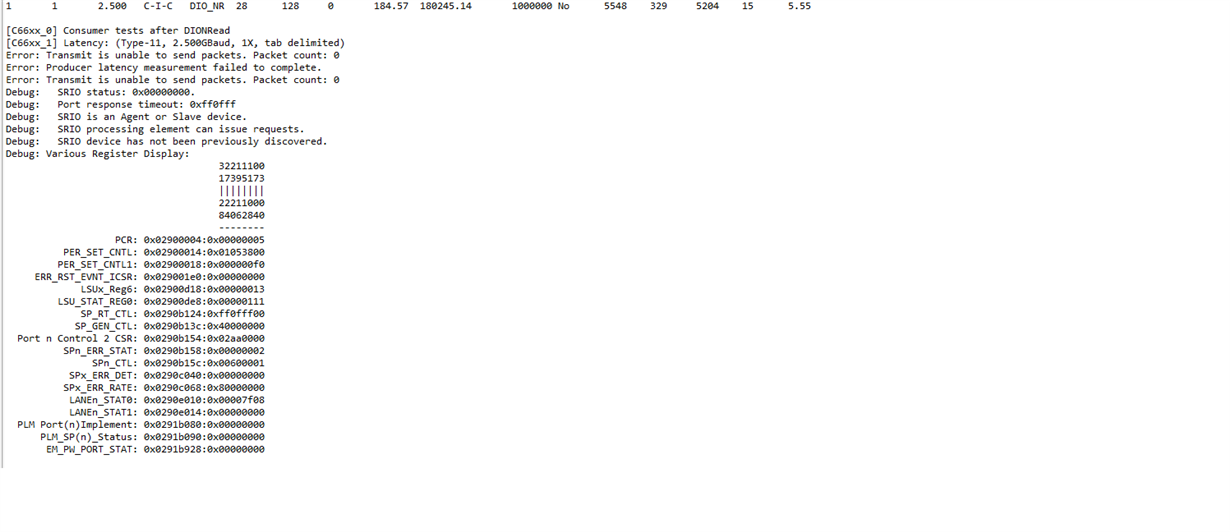

Some of the register values after we run above program in normal mode are:

rio_sp_err_stat= 0x00020002

rio_sp_ctl = 0x00600001

rio_err_det = 0x01000000

rio_sp_err_det = 0x00000001

rio_sp_lm_resp = 0x80000005

rio_comp_tag = 0x00000000

Please let us know if you need to any other register values.